| 为何CPU主频比FPGA快还要说可以帮助CPU加速? | 您所在的位置:网站首页 › 加速器占用cpu › 为何CPU主频比FPGA快还要说可以帮助CPU加速? |

为何CPU主频比FPGA快还要说可以帮助CPU加速?

|

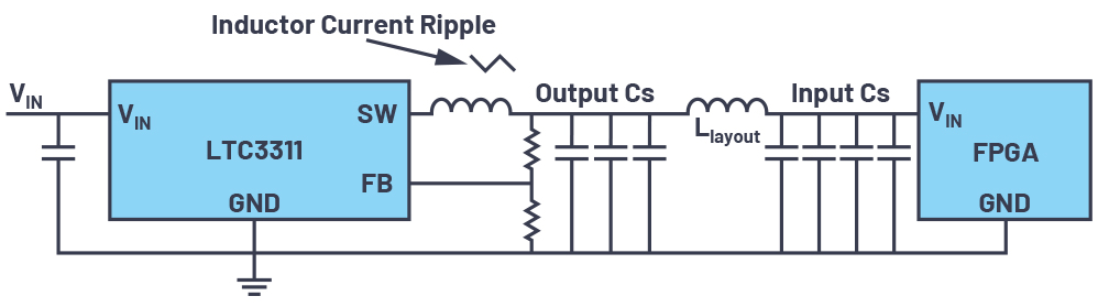

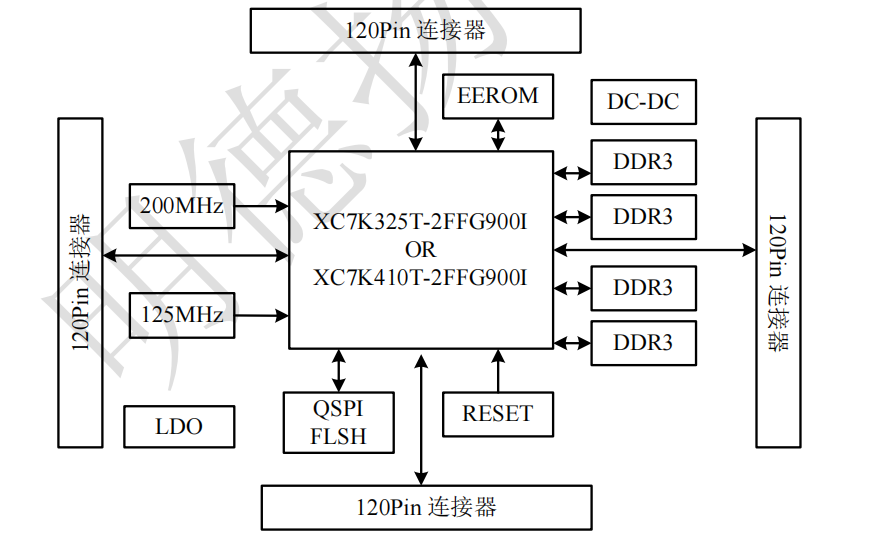

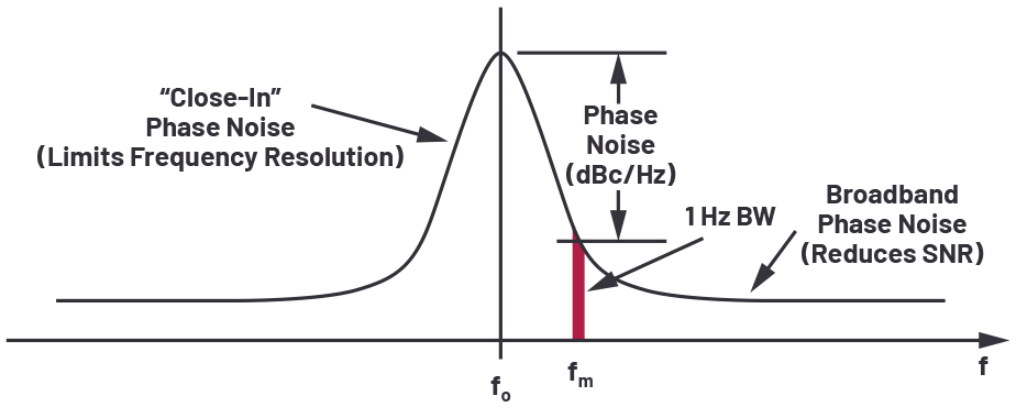

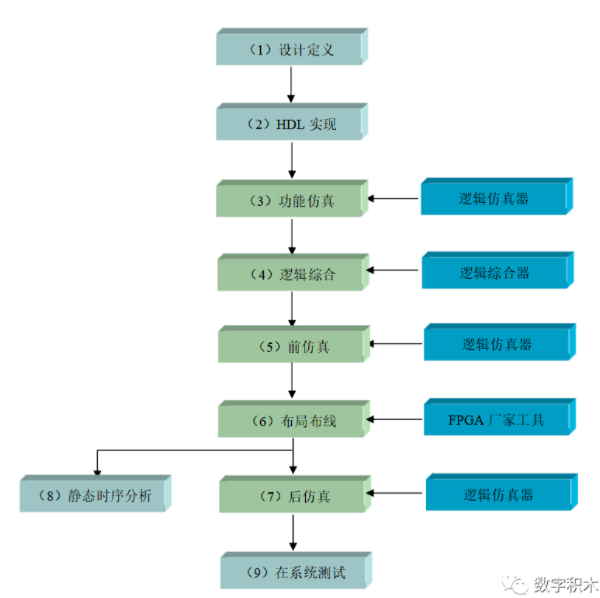

主频只是影响计算速度的一个因素,并不是全部。在执行一些计算密集型的任务场景中,FPGA的计算速度是更快的,目前FPGA作为CPU的协处理器已经广泛应用在Intel、AMD等公司的产品中。 CPU、GPU、和FPGA的比较 桌面端的CPU为冯诺依曼结构,从上图可以看出,其基本组成为控制器,Cache,和ALU。而计算单元ALU在CPU中的占比不大,所以它的并行计算能力有限。 中间的为GPU,绿色的计算单元占了绝大部分,所以并行计算能力很强。 弱点是控制能力很弱,Cache小,为了保证计算能力,就需要大量的高速DDR保证数据吞吐率。 推荐一个国外的FPGA学习网站 -- fpga4fun,里边有FPGA的介绍及26个实战项目及实现代码,非常适合入门学习! https://www.fpga4fun.com/ 正因为CPU、GPU、和FPGA在结构上的不同,也让他们在实际应用层面有所侧重。 目前主流的方案是把CPU、GPU和FPGA都集成在一个SoC中,通过片内总线互联。在执行并行计算的时候,比如进行图像处理,FPGA的优势就体现出来了,通过协作分工,使芯片的工作效率最大化。 目前的3D封装以及chiplet等技术为这样的组合提供了可实现性。 为什么FPGA计算速度会比CPU更快? 在执行大量的运算场景中,FPGA相比GPU的核心优势在于低延迟。FPGA比CPU延迟低,在本质上是体系结构的区别。FPGA同时拥有流水线并行和数据并行,而CPU几乎只有数据并行,虽然也会才有流水线设计,但深度受限。因此,FPGA 更适合做需要低延迟的流式处理,GPU 更适合做大批量同构数据的处理。 举个例子: 我们有四个全加器,每一个的进为输出连接到下一个的进位输入,这样实现的加法器被称作行波进位加法器(Ripple-Carry Adder, RCA)。其特点为: 结构特点:低位全加器的Cout连接到高一位全加器Cin 优点:电路布局简单,设计方便 缺点:高位的运算必须等待低位的运算完成 我们来看一下其关键路径的延迟: 总延迟时间:(T + T)*4 + T = 9T,推广到n位,总时间为(2n + 1)*T。 每一个全加器计算的时候必须等待它的进位输入产生后才能计算,所以四个全加器并不是同时进行计算的,而是一个一个的串行计算。这样会造成较大的延迟。 我们把这个电路改进一下:提前计算出“进位信号”,对进位信号进行分析。 这样我们就得到了一个:超前进位加法器(Carry-Lookahead Adder, CLA) 其中,C1、C2、C3、C4都由下面的电路计算好,需要3级门延迟,然后在全加器中关键路径上还有1级延迟 所以,总共有4级门延迟。 如果采用这种完全的超前进位,理论上的门延迟都是4级门延迟。 实际电路过于复杂,难以实现(C31需要32位的与门和或门!) 通常的方法:采用多个小规模的超前进位加法器拼接而成,例如,用4个8-bit的超前进位加法器连接成32-bit加法器。 所以我们需要更多的计算位宽或者更大的数组,或者矩阵的运算的时候,我们使用FPGA的优势就体现出来。再多的计算,也就是放置更多的硬件逻辑资源。 FPGA对CPU加速场景 在一些特定的应用场景下,单独使用CPU和CPU+FPGA两种方案所需处理时间的对比,可见FPGA对CPU的加速效果非常明显,甚至比单独使用CPU高出1~2个数量级! FPGA的缺点 FPGA也是有缺点的,其中之一便是开发周期长。其需要对特定的应用编写特定的FPGA。只要干的事情稍有不同,一般来说FPGA代码就要重新写一遍或者是至少要修改很多东西。如果要做的事情复杂、重复性不强,就会占用大量的逻辑资源,其中的大部分处于闲置状态。 不过,Chiplet的应用对对FPGA的开发周期有一定的优化,以下是传统FPGA开发的周期和应用chiplet的开发周期对比: 未来的方向 在现在的SoC设计中,要充分考虑不同模块的特点,FPGA 和 CPU 协同工作,充分发挥各自的长处,局部性和重复性强的归 FPGA,复杂的归 CPU。从而达到整个系统算力的最优化。 在未来,FPGA会作为协处理器和CPU、GPU共存一段时间,其主要提供以下三方面的能力: 能够提供专门的硬件加速,实现各种应用中需要的关键处理功能。 FPGA设计在性能上非常灵活,使用流水线和并行结构,适应对性能的需求变化。 协处理器能为主处理器和系统存储器提供宽带,低延迟接口。 目前,英特尔,AMD,赛灵思等公司都把FPGA作为协处理器集成在SoC中作为实际应用的硬件加速解决方案,这样的设计也使得CPU和FPGA在未来的一段时间内会共存,互相配合,赋能各种计算场景。 编辑:jq

原文标题:为什么CPU主频一般都比FPGA快,但是却说FPGA可以帮助CPU加速? 文章出处:【微信号:leezym0317,微信公众号:FPGA开源工作室】欢迎添加关注!文章转载请注明出处。 收藏 人收藏扫一扫,分享给好友 复制链接分享 评论发布评论请先 登录 相关推荐 君正X2000/X1600处理器的主要特点及应用场景 在芯片供应链紧张和客户订单急速增加的情况下,许多原本单价几块钱的芯片,价格普遍上涨了10倍、20倍甚.... 曙光携手产业伙伴构建数据中心内部节能循环

一石激起千层浪。2022年2月,国家发改委、中央网信办、工业和信息化部、国家能源局联合印发通知,同意....

曙光携手产业伙伴构建数据中心内部节能循环

一石激起千层浪。2022年2月,国家发改委、中央网信办、工业和信息化部、国家能源局联合印发通知,同意....

微操作μ-op与宏操作macro-op

英特尔逐渐改进微指令,后来加入微指令缓存即uOP cache,也有的地方叫L0级缓存,表面看来,uO....

微操作μ-op与宏操作macro-op

英特尔逐渐改进微指令,后来加入微指令缓存即uOP cache,也有的地方叫L0级缓存,表面看来,uO....

FPGA设计中时序分析的基本概念

时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中....

FPGA设计中时序分析的基本概念

时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中....

FPGA设计之时序约束

上一篇《FPGA时序约束分享01_约束四大步骤》一文中,介绍了时序约束的四大步骤。

发表于 03-18 10:29 •

16次

阅读 FPGA设计之时序约束

上一篇《FPGA时序约束分享01_约束四大步骤》一文中,介绍了时序约束的四大步骤。

发表于 03-18 10:29 •

16次

阅读

《Digital Design with Chisel》配套PPT 第三周课程

Week 3 Components and Sequential CircuitsTopics: Composing circuits out of components, sequential building blocks,...

发表于 03-18 10:00 •

1283次

阅读

富士通以混合IT构建数字化转型基石

随着数字技术的快速发展,社会正在发生怎样的变化?据预测,到2030年,CPU的计算能力和网络速度将比....

《Digital Design with Chisel》配套PPT 第三周课程

Week 3 Components and Sequential CircuitsTopics: Composing circuits out of components, sequential building blocks,...

发表于 03-18 10:00 •

1283次

阅读

富士通以混合IT构建数字化转型基石

随着数字技术的快速发展,社会正在发生怎样的变化?据预测,到2030年,CPU的计算能力和网络速度将比....

【Sipeed TangNano9K开发板试用体验】+FPGA开发初体验

前言

大家好,非常感谢电子发烧友与矽速科技基于高云GW1NR-9芯片的Sipeed TangNano9K开发板,这个是一款国产的FPGA...

发表于 03-17 11:34 •

9927次

阅读

【Sipeed TangNano9K开发板试用体验】+FPGA开发初体验

前言

大家好,非常感谢电子发烧友与矽速科技基于高云GW1NR-9芯片的Sipeed TangNano9K开发板,这个是一款国产的FPGA...

发表于 03-17 11:34 •

9927次

阅读

高速存储技术的进化:DDR和LDPPR

手机、电脑等电子设备与我们的生活密不可分,它们的使用频率高,更换周期快。消费者在购买产品时,除了考虑....

高速存储技术的进化:DDR和LDPPR

手机、电脑等电子设备与我们的生活密不可分,它们的使用频率高,更换周期快。消费者在购买产品时,除了考虑....

国内外独立服务器的区别是什么

服务器是建立网站的最基础的必不可少的东西,也是根本呢所在,所以挑选何种类型的独立服务器成为了建站者的....

发表于 03-17 10:02 •

6次

阅读

《Digital Design with Chisel》配套PPT 第二周课程

Week 2 Basic Digital Circuits in Chisel

Topics: Recap combinational and synchronous circuits with Chisel code (...

发表于 03-17 10:00 •

1188次

阅读

基于DAYU200的分布式音乐播放器

润和大禹系列HH-SCDAYU200是润和软件推出的社区内首款支持OpenHarmony富设备的.... 国内外独立服务器的区别是什么

服务器是建立网站的最基础的必不可少的东西,也是根本呢所在,所以挑选何种类型的独立服务器成为了建站者的....

发表于 03-17 10:02 •

6次

阅读

《Digital Design with Chisel》配套PPT 第二周课程

Week 2 Basic Digital Circuits in Chisel

Topics: Recap combinational and synchronous circuits with Chisel code (...

发表于 03-17 10:00 •

1188次

阅读

基于DAYU200的分布式音乐播放器

润和大禹系列HH-SCDAYU200是润和软件推出的社区内首款支持OpenHarmony富设备的....

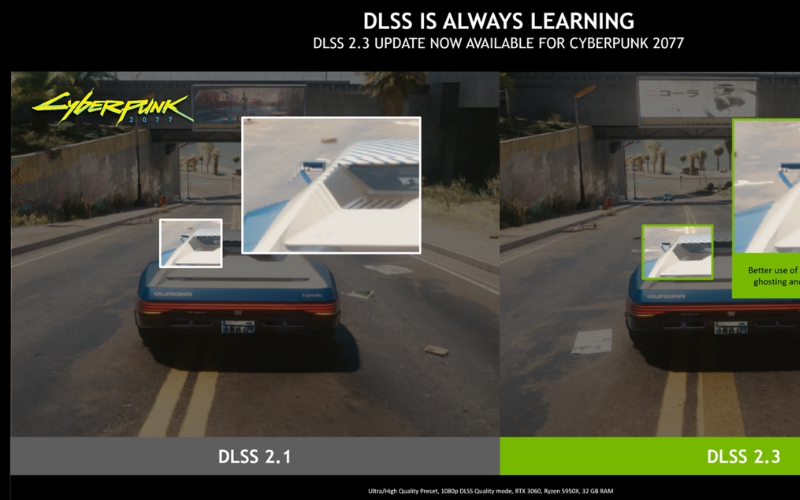

超分辨率技术大热,能不能解决物联网刚需?

随着图形渲染技术和传感器的发展,我们在日常生活中接触到的分辨率已经从过去的720p、1080p提升至.... 超分辨率技术大热,能不能解决物联网刚需?

随着图形渲染技术和传感器的发展,我们在日常生活中接触到的分辨率已经从过去的720p、1080p提升至....

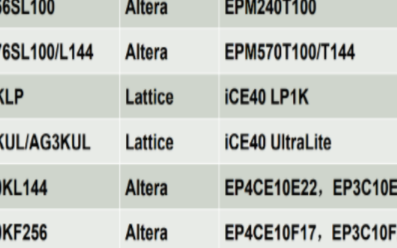

使用 fpga 简化嵌入式设计

Fpga 一直处于电信和网络创新的前沿。很长一段时间以来,在原型开发和嵌入式系统设计方面,它们一直是一个尚未开发的领域。如今...

发表于 03-16 21:46 •

405次

阅读

使用 fpga 简化嵌入式设计

Fpga 一直处于电信和网络创新的前沿。很长一段时间以来,在原型开发和嵌入式系统设计方面,它们一直是一个尚未开发的领域。如今...

发表于 03-16 21:46 •

405次

阅读

在CPU上如何同时尝试 getrandom

Jason Donenfeld 是 WireGuard 的主要开发者,同时他也是 Linux 内核随....

在CPU上如何同时尝试 getrandom

Jason Donenfeld 是 WireGuard 的主要开发者,同时他也是 Linux 内核随....

FPGA相关

准备用FPGA做电源相关的研发,比如用FPGA做开关电源,充电器,逆变器之类的。现在准备学习FPGA的相关知识,请问有没...

发表于 03-16 14:18 •

1927次

阅读

高通推出Snapdragon Ride视觉系统_瑞萨电子推出低功耗产品线进入FPGA市场

2022年1月4日,高通技术公司日推出Snapdragon Ride™平台产品组合最新产品——Sna....

FPGA相关

准备用FPGA做电源相关的研发,比如用FPGA做开关电源,充电器,逆变器之类的。现在准备学习FPGA的相关知识,请问有没...

发表于 03-16 14:18 •

1927次

阅读

高通推出Snapdragon Ride视觉系统_瑞萨电子推出低功耗产品线进入FPGA市场

2022年1月4日,高通技术公司日推出Snapdragon Ride™平台产品组合最新产品——Sna....

关于指数对比度增强FPGA实现

对比度增强是个广泛的话题,前文中关于直方图均衡的方法,其实就是一种对比度增强。而对比度增强,就是提高....

关于指数对比度增强FPGA实现

对比度增强是个广泛的话题,前文中关于直方图均衡的方法,其实就是一种对比度增强。而对比度增强,就是提高....

FPGA设计之时序约束四大步骤

本文章探讨一下FPGA的时序约束步骤,本文章内容,来源于配置的明德扬时序约束专题课视频。

发表于 03-16 09:17 •

33次

阅读 FPGA设计之时序约束四大步骤

本文章探讨一下FPGA的时序约束步骤,本文章内容,来源于配置的明德扬时序约束专题课视频。

发表于 03-16 09:17 •

33次

阅读

Altera Cyclone系列国产替代的成熟选择

从逻辑验证发展起来的FPGA,早已经成为处理器芯片家族中的重要一员,在通信、数据中心、工业领域中发挥....

Altera Cyclone系列国产替代的成熟选择

从逻辑验证发展起来的FPGA,早已经成为处理器芯片家族中的重要一员,在通信、数据中心、工业领域中发挥....

基于软件的Vitis AI 2.0加速解决方案

Vitis AI 2.0 全面发布!作为赛灵思 FPGA 和自适应 SoC 上最综合全面的基于软件的....

基于软件的Vitis AI 2.0加速解决方案

Vitis AI 2.0 全面发布!作为赛灵思 FPGA 和自适应 SoC 上最综合全面的基于软件的....

从C 到 matlab 到 FPGA,如何实现CNN的项目

经过了前面的开胃菜,项目正式开始。一步步讲解这个模型怎么玩起来的。从C 到 matlab 到 FPG....

从C 到 matlab 到 FPGA,如何实现CNN的项目

经过了前面的开胃菜,项目正式开始。一步步讲解这个模型怎么玩起来的。从C 到 matlab 到 FPG....

日常服务器的维护是怎样的

数据库经过长期的运行,需要调整数据库性能,使之进入最优化状态。数据库中的数据是最重要的,这些数据如果....

发表于 03-15 11:10 •

4次

阅读

Verilog RTL和触发器中的同步和异步复位功能分析

没有任何寄存器逻辑,RTL设计是不完整的。RTL是寄存器传输级或逻辑,用于描述依赖于当前输入和过去输....

日常服务器的维护是怎样的

数据库经过长期的运行,需要调整数据库性能,使之进入最优化状态。数据库中的数据是最重要的,这些数据如果....

发表于 03-15 11:10 •

4次

阅读

Verilog RTL和触发器中的同步和异步复位功能分析

没有任何寄存器逻辑,RTL设计是不完整的。RTL是寄存器传输级或逻辑,用于描述依赖于当前输入和过去输....

GPU、FPGA和ASIC鏖战AI推理

在深度学习的概念中,通常可以简化为两大工作流,一是训练,二是推理。两者完美融合才是一个现代化的完整深.... GPU、FPGA和ASIC鏖战AI推理

在深度学习的概念中,通常可以简化为两大工作流,一是训练,二是推理。两者完美融合才是一个现代化的完整深....

GetError与GetErrorID指令的区别与应用场景分析

在 STEP7 11 中,可以通过GetError (获取本地错误信息)或者GetErrorID (....

GetError与GetErrorID指令的区别与应用场景分析

在 STEP7 11 中,可以通过GetError (获取本地错误信息)或者GetErrorID (....

TMP411 ±1°C Programmable Remote/Local Digital Out Temperature Sensor

TMP411设备是一个带有内置本地温度传感器的远程温度传感器监视器。远程温度传感器,二极管连接的晶体管通常是低成本,NPN或PNP型晶体管或二极管,是微控制器,微处理器或FPGA的组成部分。

远程精度为±1 °C适用于多个设备制造商,无需校准。双线串行接口接受SMBus写字节,读字节,发送字节和接收字节命令,以设置报警阈值和读取温度数据。

TMP411器件中包含的功能包括:串联电阻取消,可编程非理想因子,可编程分辨率,可编程阈值限制,用户定义的偏移寄存器,用于最大精度,最小和最大温度监视器,宽远程温度测量范围(高达150°C),二极管故障检测和温度警报功能。

TMP411器件采用VSSOP-8和SOIC-8封装。

特性

±1°C远程二极管传感器

±1°C本地温度传感器

可编程非理想因素

串联电阻取消

警报功能

系统校准的偏移寄存器

与ADT7461和ADM1032兼容的引脚和寄存器

可编程分辨率:9至12位

可编程阈值限...

发表于 09-19 16:35 •

419次

阅读

TMP411 ±1°C Programmable Remote/Local Digital Out Temperature Sensor

TMP411设备是一个带有内置本地温度传感器的远程温度传感器监视器。远程温度传感器,二极管连接的晶体管通常是低成本,NPN或PNP型晶体管或二极管,是微控制器,微处理器或FPGA的组成部分。

远程精度为±1 °C适用于多个设备制造商,无需校准。双线串行接口接受SMBus写字节,读字节,发送字节和接收字节命令,以设置报警阈值和读取温度数据。

TMP411器件中包含的功能包括:串联电阻取消,可编程非理想因子,可编程分辨率,可编程阈值限制,用户定义的偏移寄存器,用于最大精度,最小和最大温度监视器,宽远程温度测量范围(高达150°C),二极管故障检测和温度警报功能。

TMP411器件采用VSSOP-8和SOIC-8封装。

特性

±1°C远程二极管传感器

±1°C本地温度传感器

可编程非理想因素

串联电阻取消

警报功能

系统校准的偏移寄存器

与ADT7461和ADM1032兼容的引脚和寄存器

可编程分辨率:9至12位

可编程阈值限...

发表于 09-19 16:35 •

419次

阅读

TMP468 具有引脚可编程的总线地址的高精度远程和本地温度传感器

TMP468器件是一款使用双线制SMBus或I 2 C兼容接口的多区域高精度低功耗温度传感器。除了本地温度外,还可以同时监控多达八个连接远程二极管的温度区域。聚合系统中的温度测量可通过缩小保护频带提升性能,并且可以降低电路板复杂程度。典型用例为监测服务器和电信设备等复杂系统中不同处理器(如MCU,GPU和FPGA)的温度。该器件将诸如串联电阻抵消,可编程非理想性因子,可编程偏移和可编程温度限值等高级特性完美结合,提供了一套精度和抗扰度更高且稳健耐用的温度监控解决方案。

八个远程通道(以及本地通道)均可独立编程,设定两个在测量位置的相应温度超出对应值时触发的阈值。此外,还可通过可编程迟滞设置避免阈值持续切换。

TMP468器件可提供高测量精度(0.75°C)和测量分辨率(0.0 625°C)。该器件还支持低电压轨(1.7V至3.6V)和通用双线制接口,采用高空间利用率的小型封装(3mm×3mm或1.6mm×1.6mm),可在计算系统中轻松集成。远程结支持-55°C至+ 150°C的温度范围。

特性

8通道远程二极管温度传感器精度:±0.75&...

发表于 09-18 16:05 •

318次

阅读

TMP468 具有引脚可编程的总线地址的高精度远程和本地温度传感器

TMP468器件是一款使用双线制SMBus或I 2 C兼容接口的多区域高精度低功耗温度传感器。除了本地温度外,还可以同时监控多达八个连接远程二极管的温度区域。聚合系统中的温度测量可通过缩小保护频带提升性能,并且可以降低电路板复杂程度。典型用例为监测服务器和电信设备等复杂系统中不同处理器(如MCU,GPU和FPGA)的温度。该器件将诸如串联电阻抵消,可编程非理想性因子,可编程偏移和可编程温度限值等高级特性完美结合,提供了一套精度和抗扰度更高且稳健耐用的温度监控解决方案。

八个远程通道(以及本地通道)均可独立编程,设定两个在测量位置的相应温度超出对应值时触发的阈值。此外,还可通过可编程迟滞设置避免阈值持续切换。

TMP468器件可提供高测量精度(0.75°C)和测量分辨率(0.0 625°C)。该器件还支持低电压轨(1.7V至3.6V)和通用双线制接口,采用高空间利用率的小型封装(3mm×3mm或1.6mm×1.6mm),可在计算系统中轻松集成。远程结支持-55°C至+ 150°C的温度范围。

特性

8通道远程二极管温度传感器精度:±0.75&...

发表于 09-18 16:05 •

318次

阅读

|

【本文地址】