| 【网络BSP开发经验】交换芯片驱动开发1(RTL8306MB交换芯片驱动开发) | 您所在的位置:网站首页 › 交换机原理图注意点 › 【网络BSP开发经验】交换芯片驱动开发1(RTL8306MB交换芯片驱动开发) |

【网络BSP开发经验】交换芯片驱动开发1(RTL8306MB交换芯片驱动开发)

|

文章目录

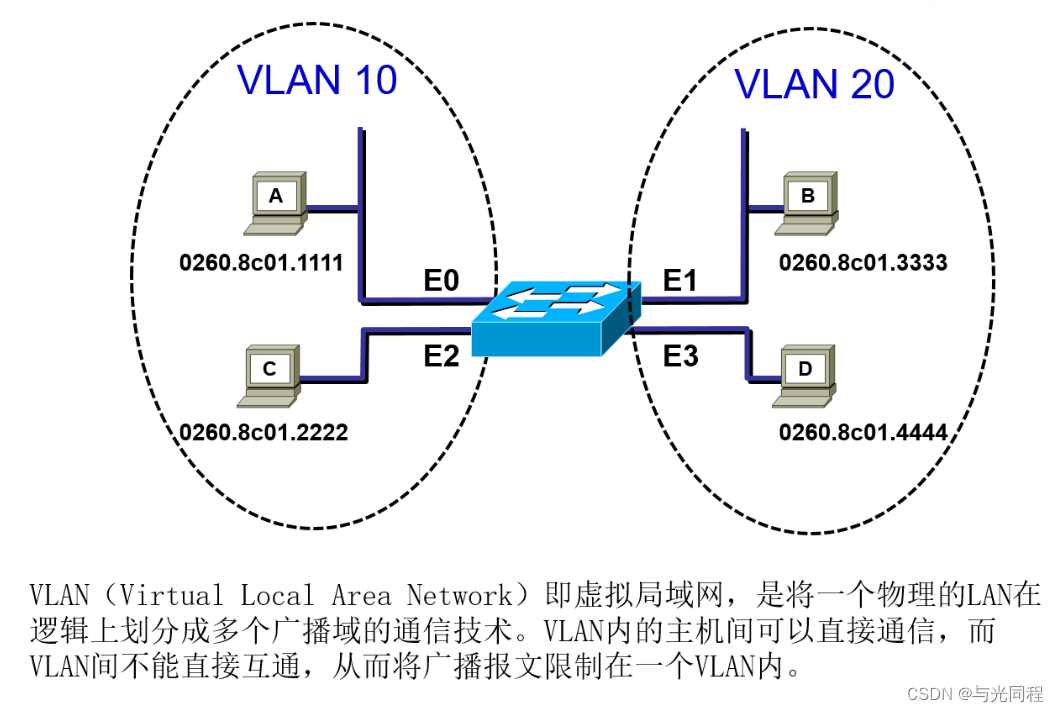

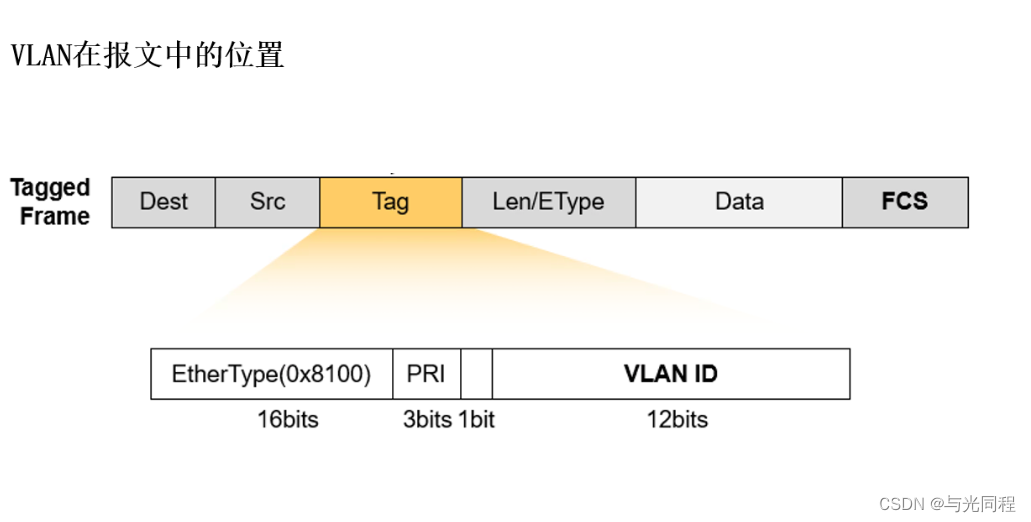

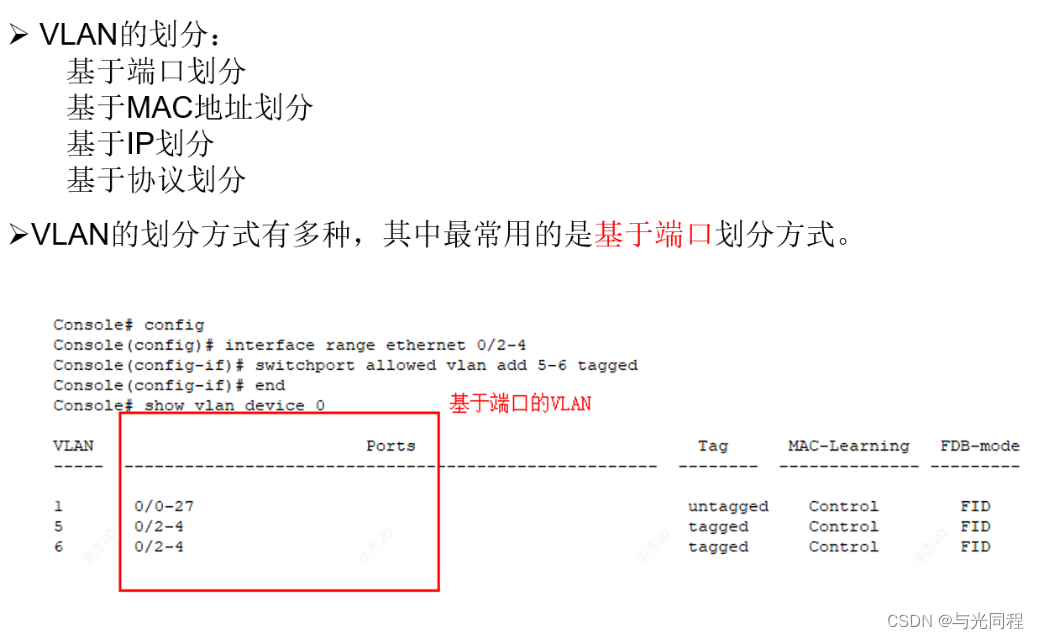

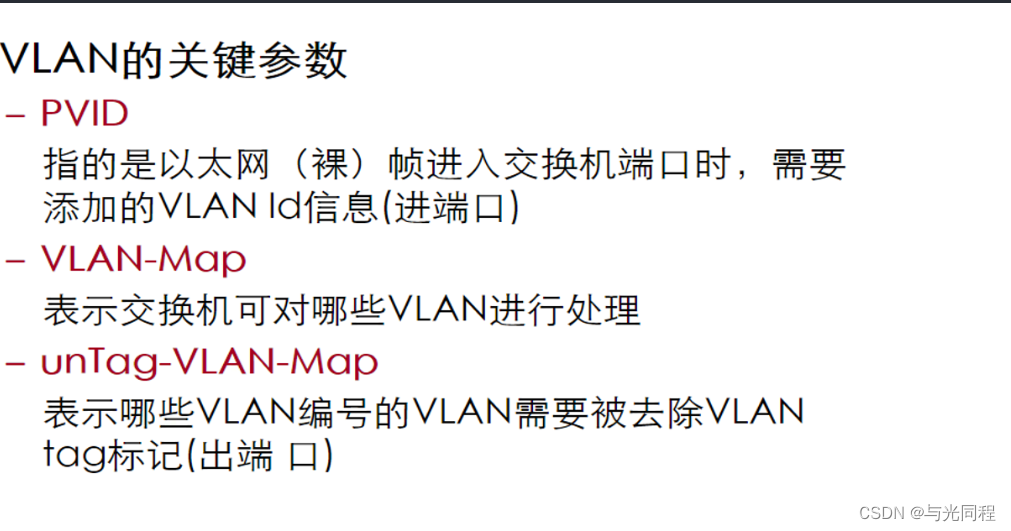

交换机基础知识交换机处于网络中的位置以太网帧结构端口二层转发原理VLAN

典型网络接口分析SMIMII接口RMII接口GMII接口

典型交换芯片分析RTL8306MB

交换芯片调试过程交换芯片SDK移植问题背景问题解决

交换机基础知识

交换机处于网络中的位置

SMI 是MMI管理总线具有 MDIO和MDC两根线,它允许带有smi的外部设备控制PHY的状态以及内部寄存器。

MII(Media Independent interface)即介质无关接口,它是IEEE-802.3定义的行业标准,是MAC与PHY之间的接口。MII数据接口包含16个信号和2个管理接口信号,如下图所示:

RMII接口有12个信号线,节省了一半的数据线 ,主要包括四个部分。一是从MAC层到物理层的发送数据接口,二是从MAC层到物理层的接收数据接口,三是物理层与MAC层之间时钟接口,四是MAC层和物理层之间数据管理的MDIO/MDC接口。

其中CRS_DV是MII中RX_DV和CRS两个信号的合并,当物理层接收到载波信号后CRS_DV变得有效,将数据发送给RXD。当载波信号消失后,CRS_DV会变为无效。在100M以太网速率中,MAC层每个时钟采样一次RXD[1:0]上的数据,在10M以太网速率中,MAC层每10个时钟采样一次RXD[1:0]上的数据,此时物理层接收的每个数据会在RXD[1:0]保留10个时钟。 GMII接口GMII(Gigabit Media Independant Interface),千兆MII接口。GMII采用8位接口数据,工作时钟125MHz,因此传输速率可达1000Mbps。同时兼容MII所规定的10/100 Mbps工作方式。GMII接口数据结构符合IEEE以太网标准,该接口定义见IEEE 802.3-2000。信号定义如下:

综合分析网络接口都具有几根共性的线: 时钟线:都是由PHY侧向MAC侧提供时钟 SMI线:管理PHY寄存器 RXDV: PHY侧向MAC侧告知数据发送 TXEN:MAC侧向PHY侧告知数据发送 典型交换芯片分析CPU集成MAC外接switch芯片,switch内部一般是N个PHY和N+1个MAC,通过CPU的MAC与Switch的MAC使用MII/RMII等接口MAC-MAC方式连接

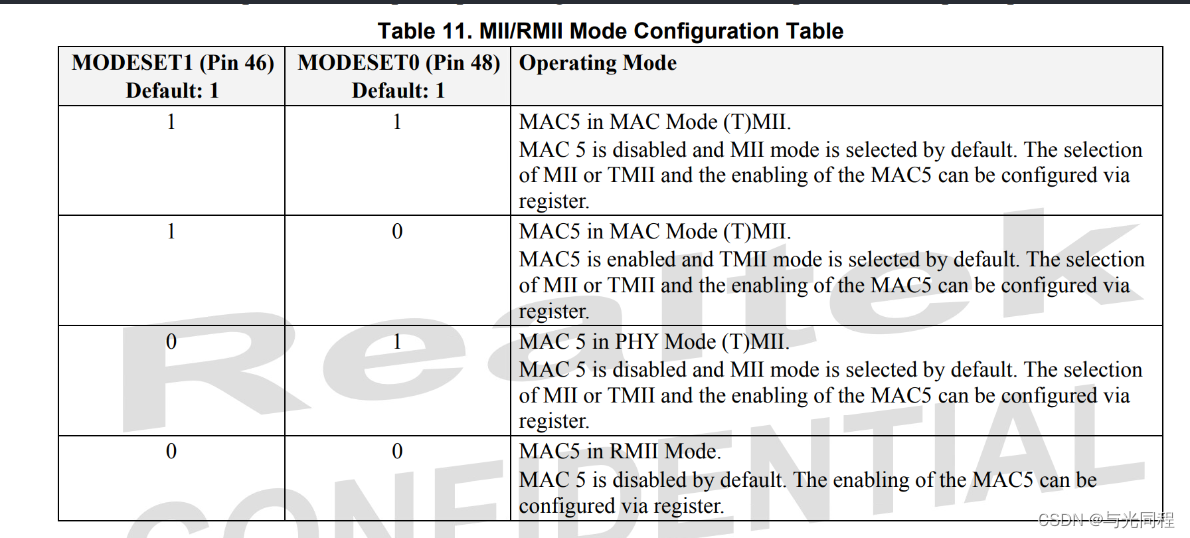

为了可以进行这样的连接,switch与CPU连接的那个MAC口通常可以配置成PHY模式,这个时候从CPU的角度来看,switch与之连接的端口可以看成一个PHY。 RTL8306MBRTL8306MB-CG是6端口10 / 100M以太网交换机控制器,将用于10Base-T和100Base-TX操作的内存,六个MAC和五个物理层收发器集成到单个芯片中。它支持(T)MII / RMII接口,以使外部设备连接到第六个MAC。外部设备可以是路由引擎,HomePNA,HomePlug或VDSL收发器,具体取决于应用程序。 特征: 基本切换功能 具有存储器和收发器的6端口开关控制器,用于10Base-T和100Base-TX 无阻塞线速收发,无阻塞头转发 兼容IEEE 802.3 / 802.3u自动协商 内置用于数据包缓冲区的高效SRAM,具有2K条目查找表 2048字节最大数据包长度 完全支持流量控制 半双工:背压流量控制 全双工:IEEE 802.3x流控制 支持与外部MAC或PHY的(T)MII / RMII接口连接 支持最多16个VLAN,并且支持VLAN学习,带有四个独立的IVL过滤。 RTL8306MB可以通过硬件管脚将MAC5 配置成三种模式:MAC MODE(MII ) , PHY MODE(MII) ,RMII MODE。

其中RTL8306E管理接口为MDC/MDIO,MDC为时钟,MDIO为传输数据…源代码使用两个GPIO引脚来模拟MDC/MDIO信号。将此驱动程序移植到客户平台需要创建文件mdcmdio.c和mdcmdio.h。在这些文件中, 需要实现smi通信逻辑 。如果已经有SMI读写接口再包装一层即可。

此外还要注意另一个问题,即在SMI读取和写入期间,防止CPU被打断 ,因此在SMIREAD和SMIWRITE中,需要关闭中断以及调度。 问题背景

在这个项目中的rtl8306MB的mac5 就是被配置成RMII MODE ,首先在进行SMI总线调试的时候非常顺利,可以使用SMI读出chipid , 读写交换芯片配置信息。但是在调试RMII总线的过程中发现switch的MAC5没有任何收发包的记录,cpu也没有任何收发包的记录。所以就准备先用示波器寻找原因。 问题解决我们首先判断RTL8306MB没有配置成RMII模式,也就是说时钟可能没有通过时钟线从RTL8306MB芯片传输到CPU中,所以首先通过示波器读取时钟信号,在硬件上需要断开时钟信号,然后分别读取时钟线两边的信号:

读取后发现switch侧有50M时钟,MAC侧无时钟,说明RMII模式配置正常。 然后读取数据线上的数据,因为数据线是独立的,所以每一边只要测差分信号的其中一根就行: 我们首先通过电脑向switch芯片发包然后读取switch芯片和CPU之间的 TXD数据线:

然后使用cpu通过发包函数,向switch发包:

发现 两边的数据线上都是有数据的,这就说明两边都是正常进行发送的。 然后测试TXEN,RXDV TXEN:

发现TXEN有信号,而RXDV一直没有信号。 所以判断硬件上是不是将TXEN和对端的RXDV 接了起来,为了判断是否是这个问题,我们将TXEN线上的串阻卸下然后在串阻的两端同时检测到使能信号:

所以MAC侧和PHY侧的使能信号竟然同时出现在了TXEN信号上。所以就可以确定就是将两端的TXEN和RXDV接起来了。飞线之后发现GMAC收发包正常。 查看芯片手册:

从芯片手册上来看,硬件同事犯了一个非常容易犯的错误,因为在RMII默认就是PHY模式,所以将TXEN,和RXDV搞反了,导致了两端的TXEN接到了对端的RXDV上,导致两端都无法收到使能信号,导致GMAC通信异常。 |

【本文地址】

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-GzIAZnbW-1678890143298)(image/驱动开发学习13交换芯片开发/1675856042249.png)]](https://img-blog.csdnimg.cn/987dc026cd7d45cd81ef72130853594f.png)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-mm7MPlIj-1678890143298)(image/驱动开发学习13交换芯片开发/1675856166581.png)]](https://img-blog.csdnimg.cn/27cb1784621943a885a08d1a3e5e3f99.png)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-B74TPh2F-1678890143299)(image/驱动开发学习13交换芯片开发/1675856211989.png)]](https://img-blog.csdnimg.cn/3a828470a6fb436db3a250eeac25eade.png)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-taqk0Cd8-1678890143299)(image/驱动开发学习13交换芯片开发/1675856241083.png)]](https://img-blog.csdnimg.cn/d8840fd7be4341eeaa6c811f439a05be.png)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-JGym2LuS-1678890143300)(image/驱动开发学习13交换芯片开发/1675856272949.png)]](https://img-blog.csdnimg.cn/d0b3b69034b0499c8e03b4bc4d44958d.png)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-BTGOFPDx-1678890143300)(image/驱动开发学习13交换芯片开发/1675856302211.png)]](https://img-blog.csdnimg.cn/f32eeae151524fd8bc593eb9f56e9836.png)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-SaJKPnb4-1678890143300)(image/驱动开发学习13交换芯片开发/1675856322129.png)]](https://img-blog.csdnimg.cn/d6a15e11fee44a1b9a8cf4a110c044e5.png)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-GeNfnFmJ-1678890143300)(image/驱动开发学习13交换芯片开发/1675856355680.png)]](https://img-blog.csdnimg.cn/68159c12a6c646a3bd48a5e28a11568f.png)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-BtNjA4Us-1678890143301)(image/驱动开发学习13交换芯片开发/1675856377399.png)]](https://img-blog.csdnimg.cn/5bba9b04e88e48f5b094198fc70122a4.png)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-6AlXHP1k-1678890143301)(image/驱动开发学习13交换芯片开发/1675856393633.png)]](https://img-blog.csdnimg.cn/4d70a610cddf4ec6a7a2521391300683.png)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-uwkl9m4y-1678890143301)(image/驱动开发学习13交换芯片开发/1675856432980.png)]](https://img-blog.csdnimg.cn/a83e6bcdf988451e8c6fd9a650483aa1.png)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-g3pRlF1D-1678890143302)(image/驱动开发学习13交换芯片开发/1675856454445.png)]](https://img-blog.csdnimg.cn/5427acd21bc84ecdb37c2a96f446b4e4.png)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-cgmyhpFi-1678890143305)(image/驱动开发学习13交换芯片开发/1675857461740.png)]](https://img-blog.csdnimg.cn/0dde1f40cc1b423aba9778cd22faceb2.png)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-j5F8URWO-1678890143305)(image/驱动开发学习13交换芯片开发/1678433133794.png)]](https://img-blog.csdnimg.cn/cedadbb7bd51475c9e30c9816a515133.png)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-DHrHQgSf-1678890143305)(image/驱动开发学习13交换芯片开发/1678433173162.png)]](https://img-blog.csdnimg.cn/7f418995c60042af83a4811f8bbea35a.png)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-eduz8sBF-1678890143305)(image/驱动开发学习13交换芯片开发/1678431840207.png)]](https://img-blog.csdnimg.cn/7df8453f0e444893a544e8798fcdfbfc.png)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-34nSHUbs-1678890143306)(image/驱动开发学习13交换芯片开发/1678433209732.png)]](https://img-blog.csdnimg.cn/c1e9d8cc505445aabc8358638af826e2.png)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-ytadFdxY-1678890143306)(image/驱动开发学习13交换芯片开发/1678433386429.png)]](https://img-blog.csdnimg.cn/72ff7b74ec2a4a35bc1032b16556c4db.png)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-ZWaUb0IP-1678890143306)(image/驱动开发学习13交换芯片开发/1678438731786.png)]](https://img-blog.csdnimg.cn/abad0c6000c647868499a339b49c2ddf.png)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-p6rLUE3O-1678890143306)(image/驱动开发学习13交换芯片开发/1678434225792.png)]](https://img-blog.csdnimg.cn/17cd4a46f4914848be59a2769a6b2d28.png)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-na1kPJKb-1678890143306)(image/驱动开发学习13交换芯片开发/1678434501189.png)]](https://img-blog.csdnimg.cn/06d12fb23dee4b2baac49c6966044fe5.png)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-rD7yCsFR-1678890143307)(image/驱动开发学习13交换芯片开发/1678434514692.png)]](https://img-blog.csdnimg.cn/aebc010fd67c48269e49d935f30b223c.png)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-D5P3w4Az-1678890143307)(image/驱动开发学习13交换芯片开发/1678434541515.png)]](https://img-blog.csdnimg.cn/8f3e9dd3a27a40bbaae49e1160f2fd2d.png)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-Z6BR6ygT-1678890143307)(image/驱动开发学习13交换芯片开发/1678437814211.png)]](https://img-blog.csdnimg.cn/3606b2f9d4ea4768b906534a4d08561d.png)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-wrUCjYbP-1678890143307)(image/驱动开发学习13交换芯片开发/1678435853921.png)]](https://img-blog.csdnimg.cn/40b27705b429488eae3ce228b7ab6996.png)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-yUPDG6UI-1678890143307)(image/驱动开发学习13交换芯片开发/1678436146396.png)]](https://img-blog.csdnimg.cn/1e7652dab3344ad4ab737ccc6a370284.png)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-949A7oF6-1678890143307)(image/驱动开发学习13交换芯片开发/1678436192826.png)]](https://img-blog.csdnimg.cn/cb5161e1fff940e2aba34afeb618e952.png)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-URrvKNh2-1678890143307)(image/驱动开发学习13交换芯片开发/1678436203179.png)]](https://img-blog.csdnimg.cn/e84470f62b24455a99deed47ddd86026.png)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-5mJCLnI1-1678890143308)(image/驱动开发学习13交换芯片开发/1678436214526.png)]](https://img-blog.csdnimg.cn/b807471eb892459e8bad99fb9b476b92.png)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-S0R5NFEQ-1678890143308)(image/驱动开发学习13交换芯片开发/1678436291215.png)]](https://img-blog.csdnimg.cn/39ceaaa2355d4a218648ec6d5caf1bb6.png)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-7KvARrZQ-1678890143308)(image/驱动开发学习13交换芯片开发/1678437114418.png)]](https://img-blog.csdnimg.cn/c71ad882f38246ba8fde3d794e37da78.png)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-GXOWJvPc-1678890143308)(image/驱动开发学习13交换芯片开发/1678437496966.png)]](https://img-blog.csdnimg.cn/60f8c1e498a74ee385b55a1451602b74.png)