| FPGA学习记录 | 您所在的位置:网站首页 › vivado文件后缀 › FPGA学习记录 |

FPGA学习记录

|

目录

前言工程创建工程仿真引脚配置编译

前言

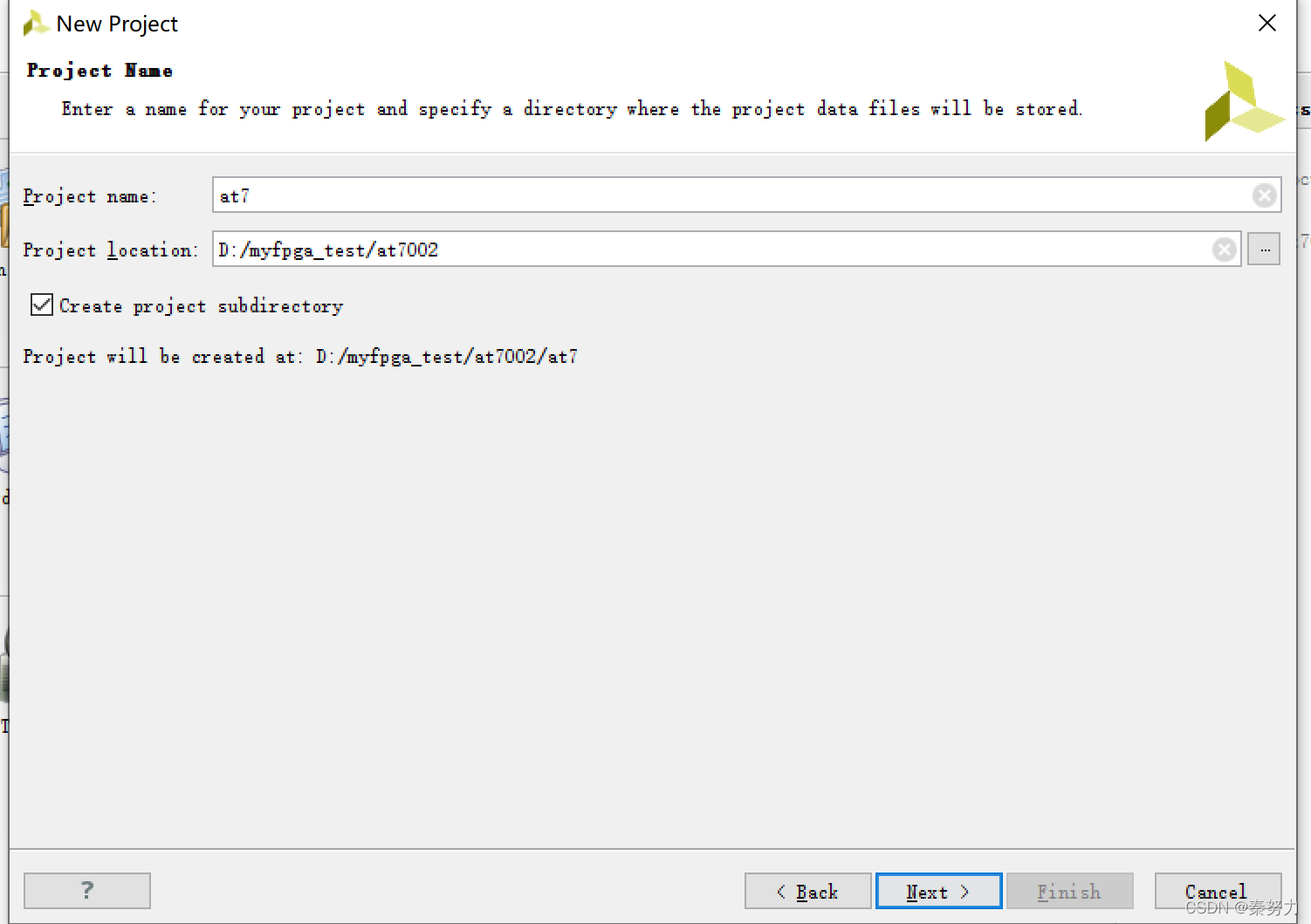

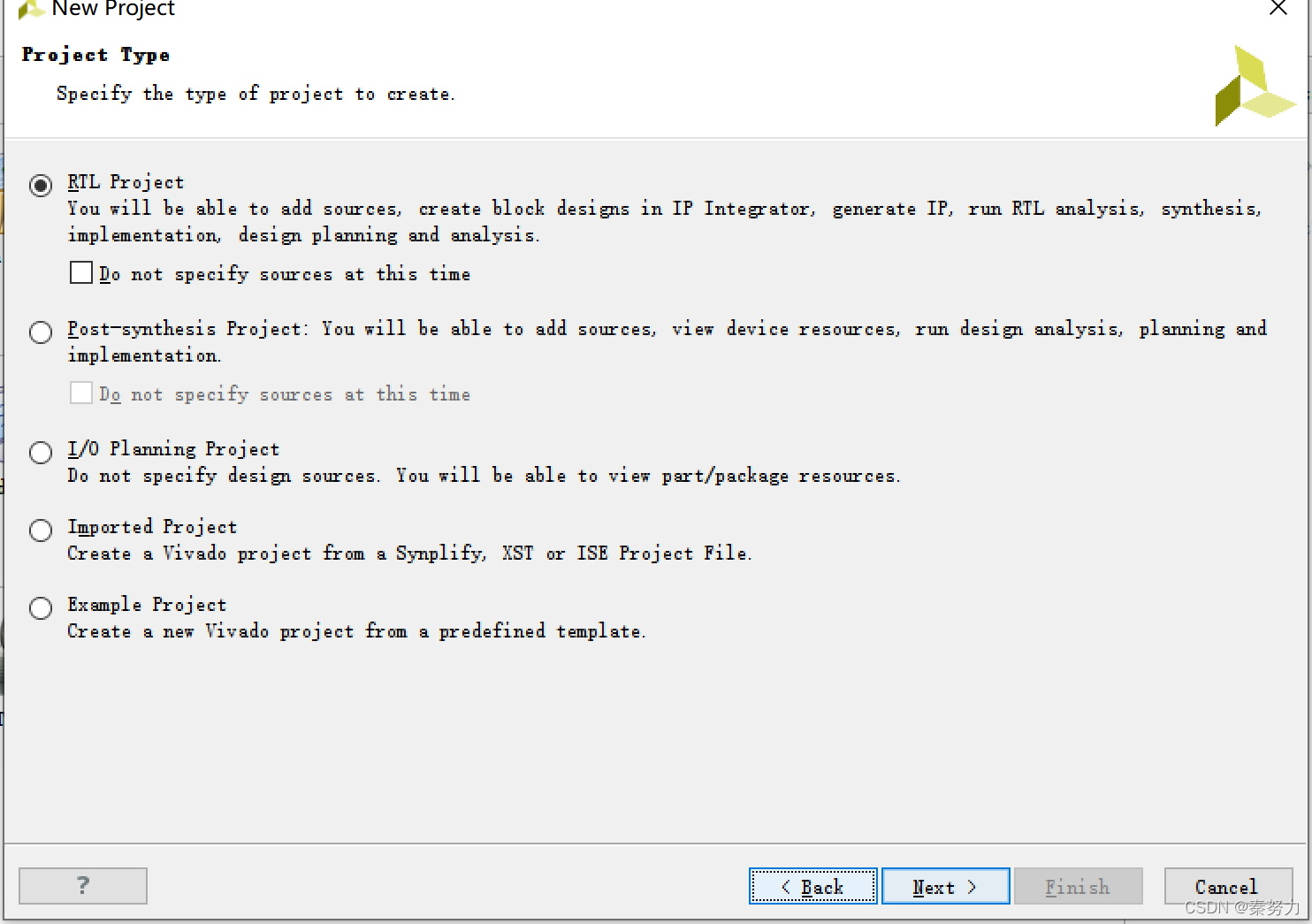

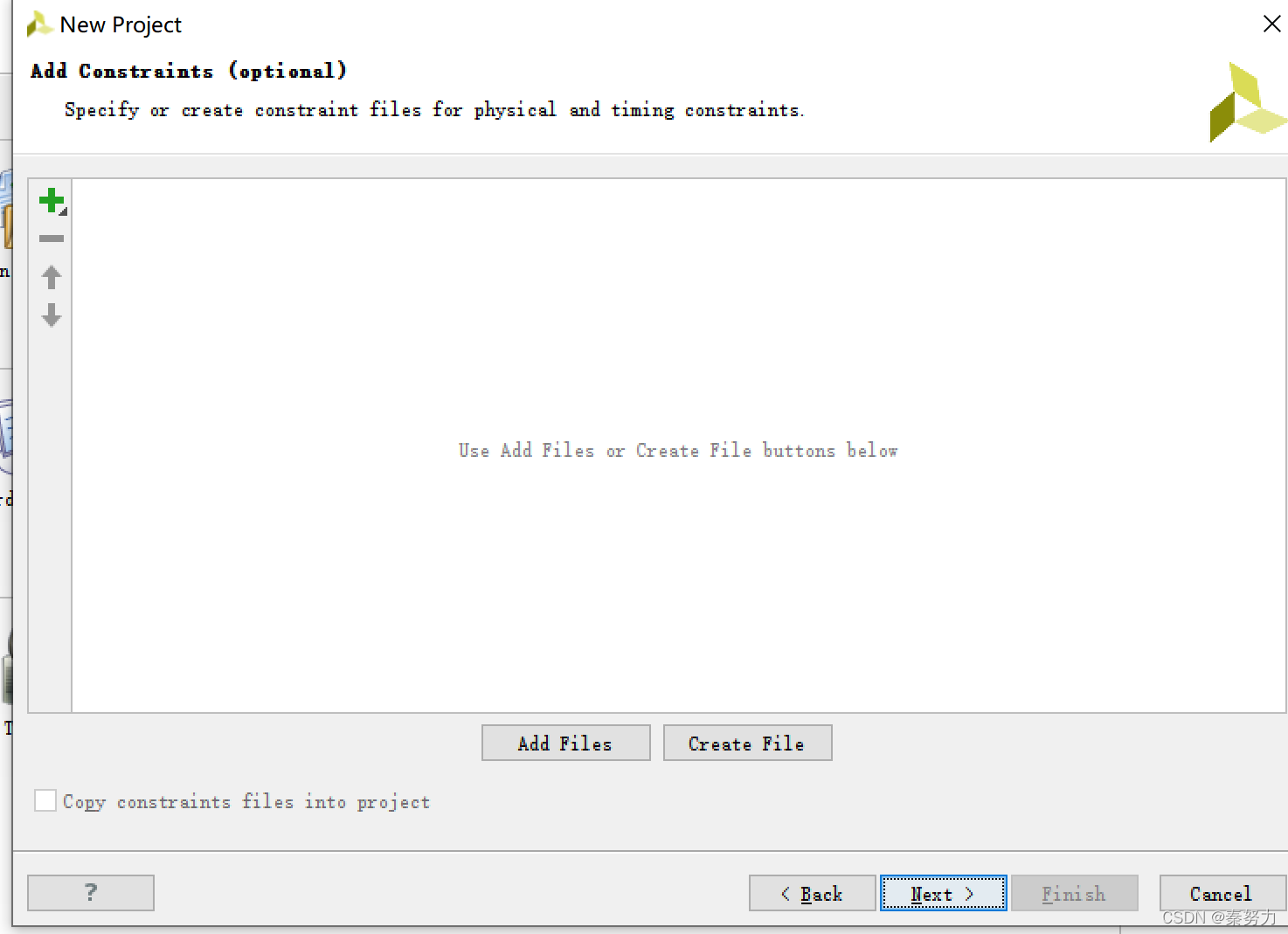

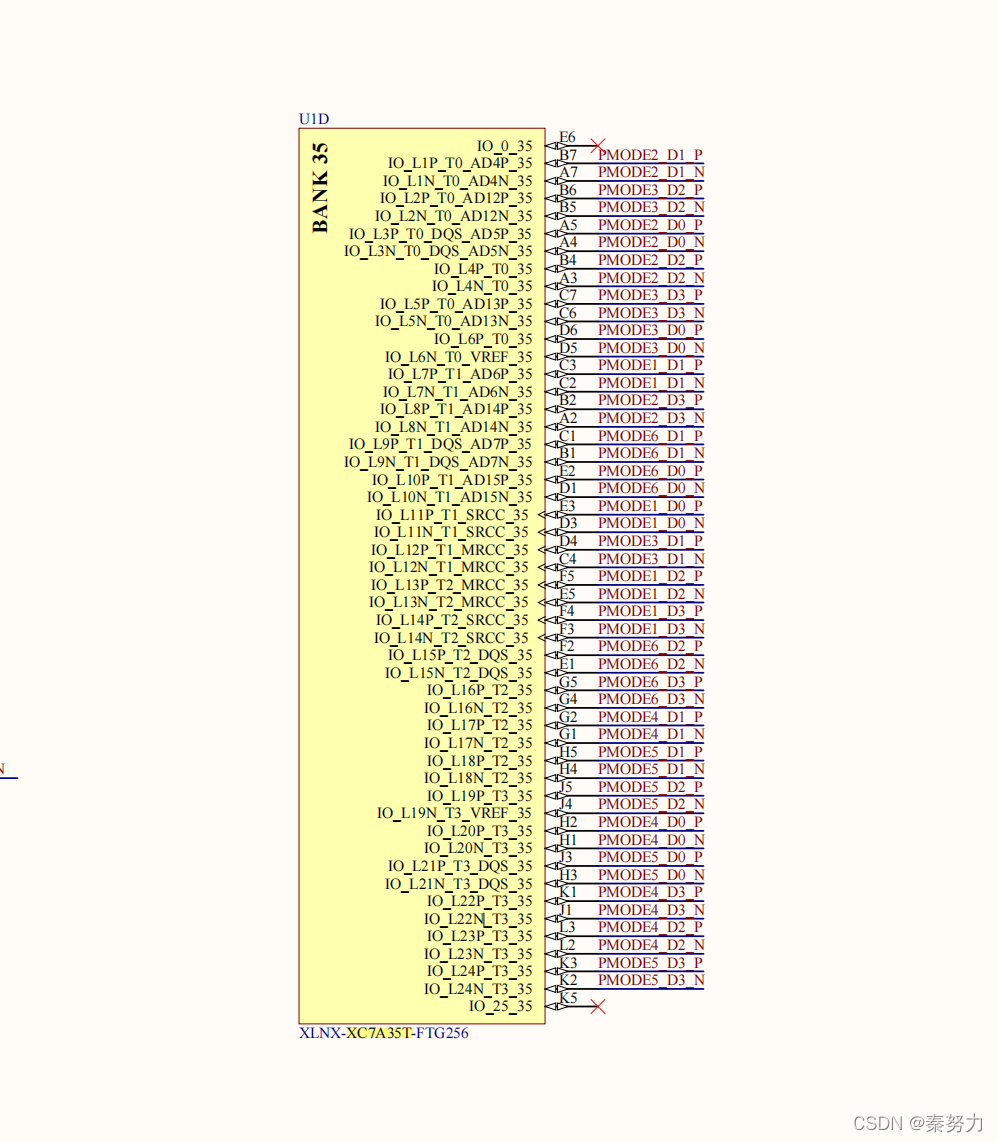

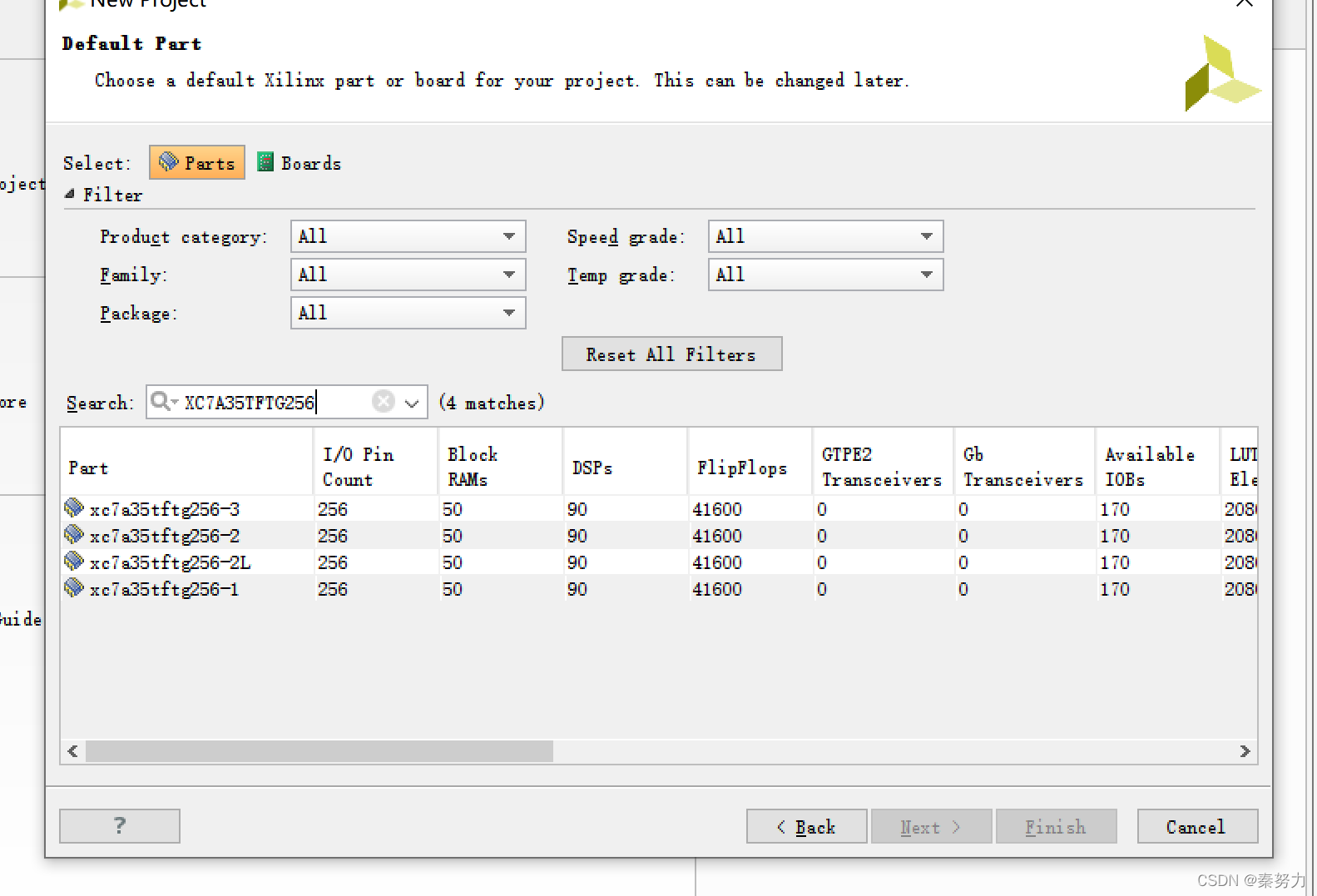

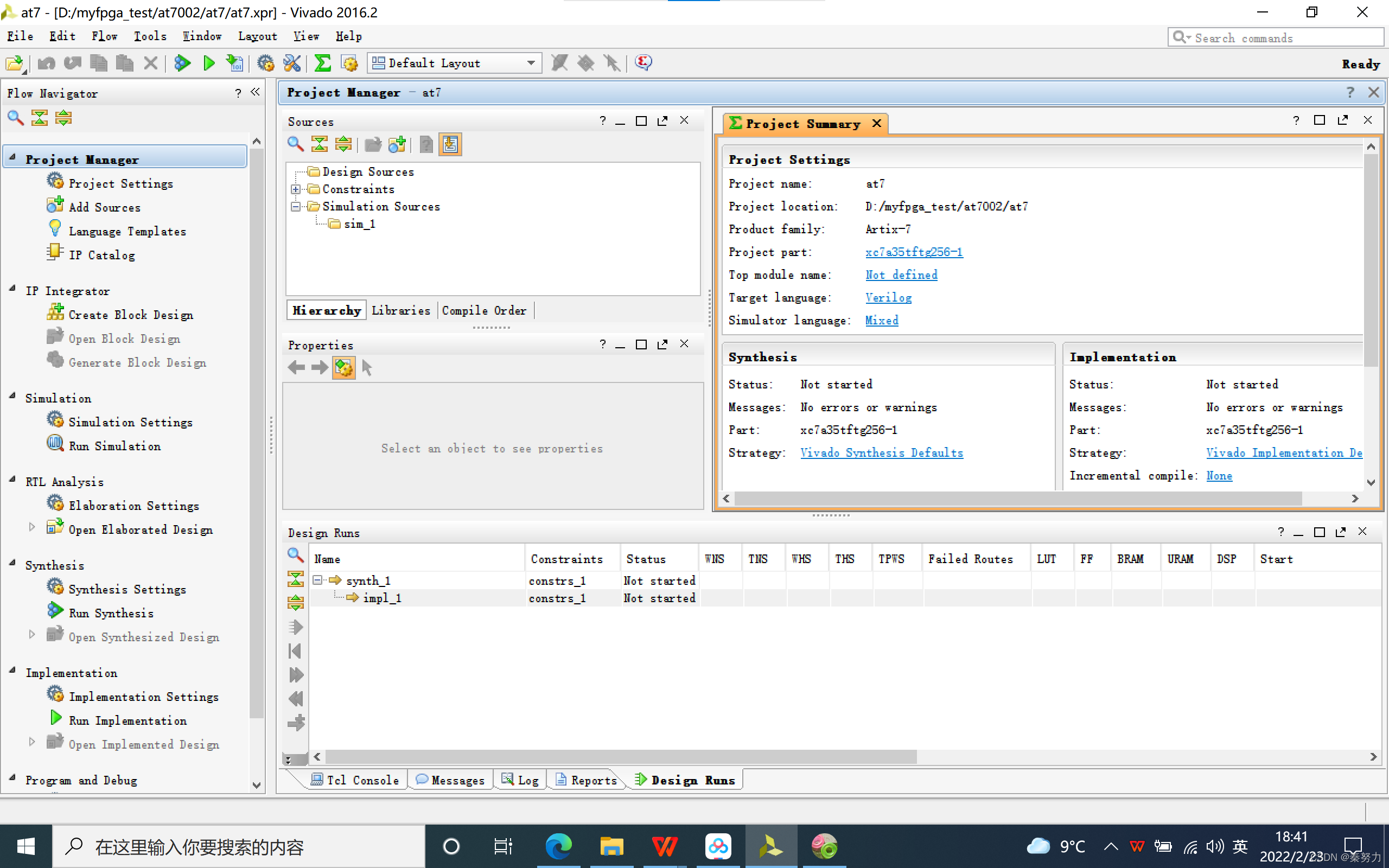

本系列文章作为对特权同学《深入浅出玩转FPGA》课程学习的记录,对课程内容进行总结,比记录遇到的问题与解决办法,以此见证个人FPGA学习历程。这篇文章主要对工程的创建、仿真、编译、烧录过程进行总结,不足之处,还请各位在评论区指出,谢谢! 开发板:SF-AT7 软件平台:Vivado 2016.2 工程创建 在创建工程之前建立一个新的文件夹用于存放之后建立的工程,注意路径中不要出现中文、标点符号等,英文、下划线允许出现。 如图所示,在myfpga_test下建立at7002的文件夹 - 打开之前安装好的vivado,点击create new project 如图所示,在myfpga_test下建立at7002的文件夹 - 打开之前安装好的vivado,点击create new project 在弹出的对话框中修改工程名与工程存放的路径,这里将工程路径直接定位到之前新建立的文件夹即可,然后点击next 在弹出的对话框中修改工程名与工程存放的路径,这里将工程路径直接定位到之前新建立的文件夹即可,然后点击next  下一步选择创建RTL project,即为正常的FPGA逻辑设计工程,RTL全拼为Register Transfer Level,为寄存器转换级。在RTL级,集成电路是由一组寄存器和寄存器之间的逻辑操作构成,RTL是用硬件描述语言(Verilog 或VHDL)描述理想达到的功能,不同于门电路,所以我们选择创建RTL 级工程。 下一步选择创建RTL project,即为正常的FPGA逻辑设计工程,RTL全拼为Register Transfer Level,为寄存器转换级。在RTL级,集成电路是由一组寄存器和寄存器之间的逻辑操作构成,RTL是用硬件描述语言(Verilog 或VHDL)描述理想达到的功能,不同于门电路,所以我们选择创建RTL 级工程。  下一步是添加HDL源文件,如果已经设计好源文件,点击add source可以直接添加,若没有直接next; 接着添加IP核、约束文件,如果都没有直接跳过点击next(后续可以在工程界面直接添加); 下一步是添加HDL源文件,如果已经设计好源文件,点击add source可以直接添加,若没有直接next; 接着添加IP核、约束文件,如果都没有直接跳过点击next(后续可以在工程界面直接添加);  其次,添加FPGA的型号,这要根据自己手中已有板子型号进行添加,一般型号的确定在板子提供的原理图上有,以本次工程使用的a7板子为例,打开原理图,找到FPGA的型号:XC7A35TFTG256 其次,添加FPGA的型号,这要根据自己手中已有板子型号进行添加,一般型号的确定在板子提供的原理图上有,以本次工程使用的a7板子为例,打开原理图,找到FPGA的型号:XC7A35TFTG256  在搜索框中搜索该型号:(后面的-1、-2表示速度等级,A7速度等级为1,所以选择最下面的FPGA型号) 在搜索框中搜索该型号:(后面的-1、-2表示速度等级,A7速度等级为1,所以选择最下面的FPGA型号)  最后,点击finish,完成工程创建,创建后vivado页面如下: 最后,点击finish,完成工程创建,创建后vivado页面如下:

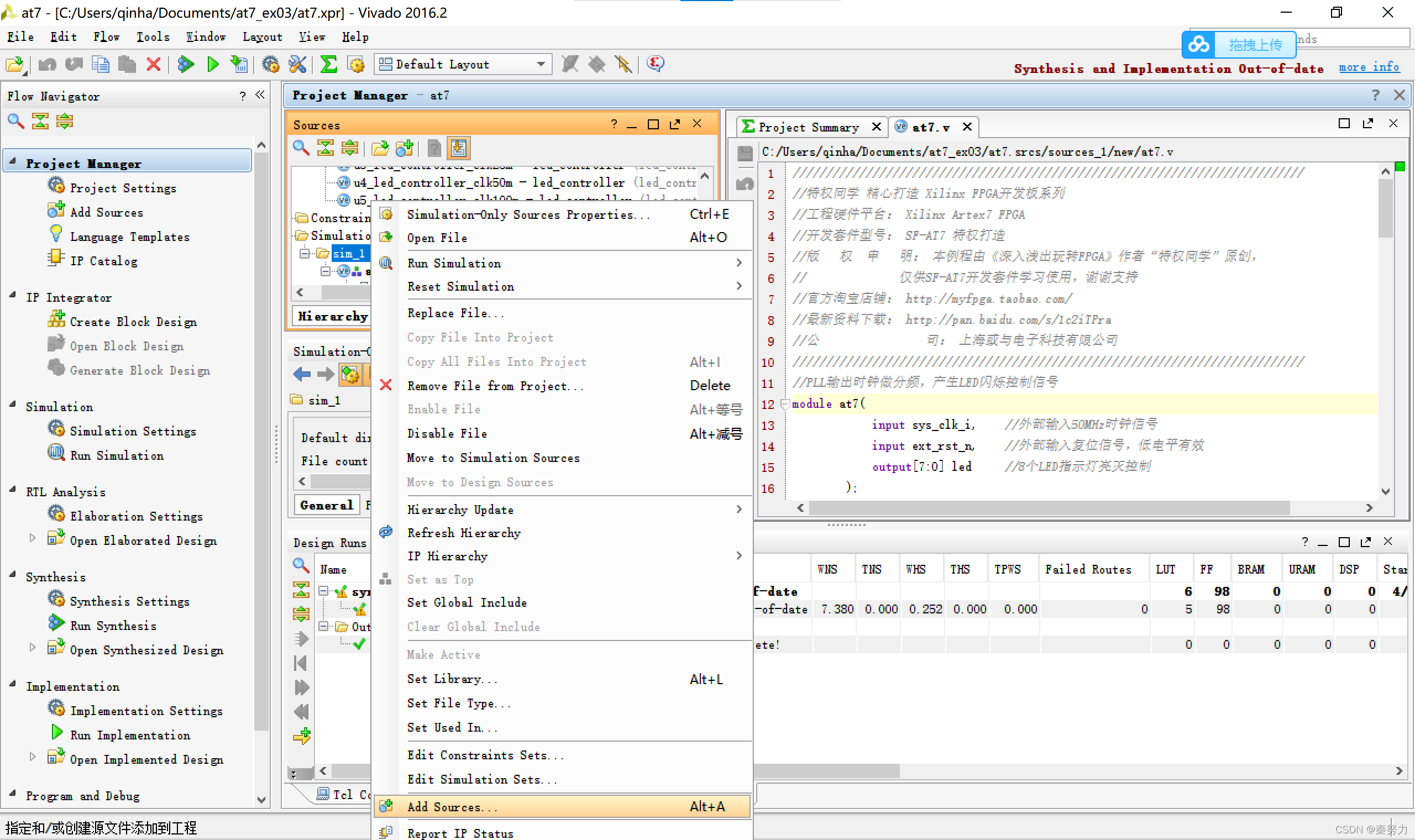

注意源文件名称要与工程名称保持一致,因为该源文件作为顶层文件,在源文件中完成相应功能描述 工程仿真当设计文件按照功能要求编写完毕后,进行工程的仿真,在仿真开始之前要有仿真文件,仿真文件对当前设计做验证。若没有仿真文件,右键sim_1,选择add source即可添加,添加方式和添加源文件一样。仿真文件的编写这里不赘述。

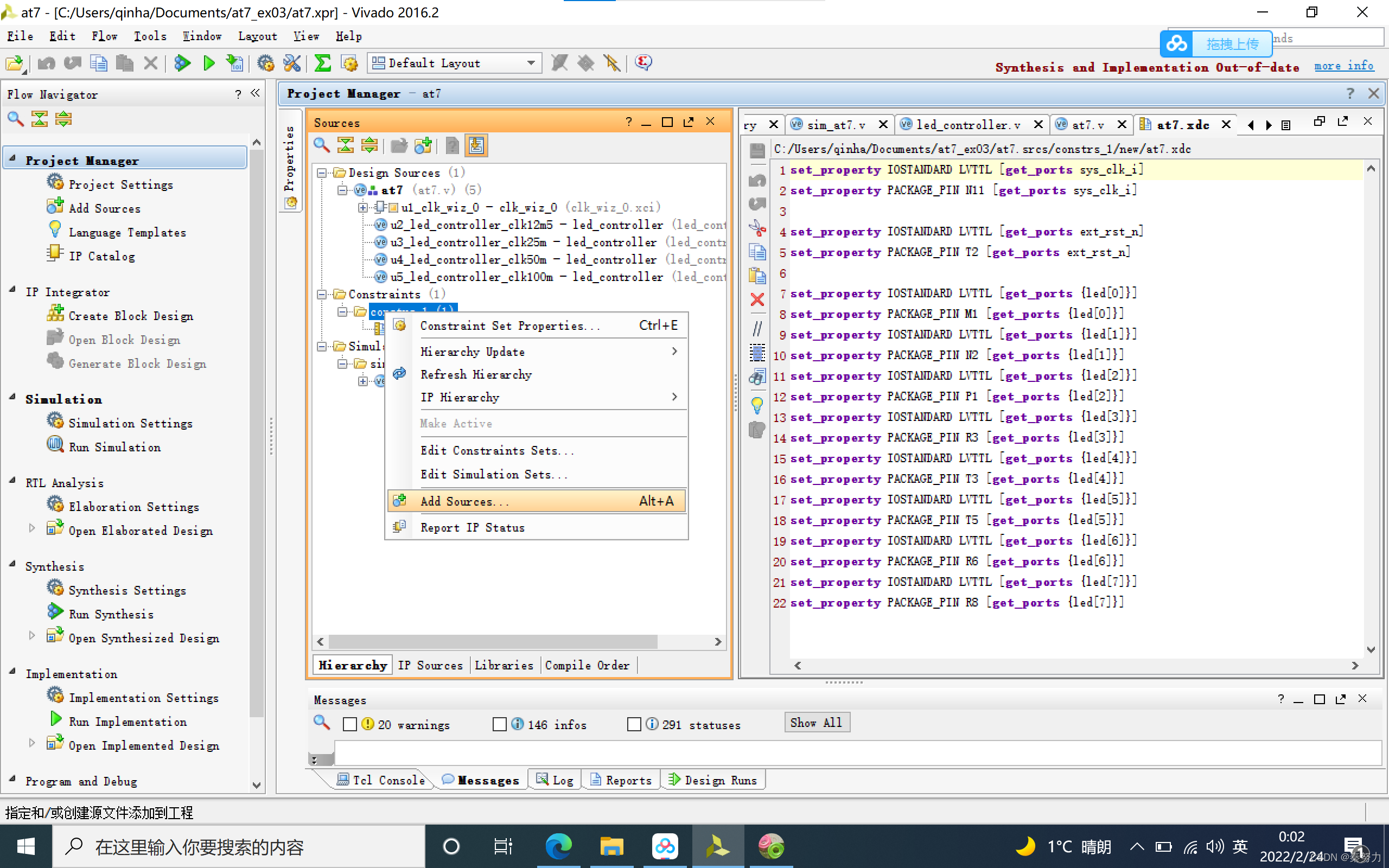

通过仿真观察波形符合功能要求是,就要开始工程综合,将代码烧录到FPGA开发板中看实际的运行效果。首先要进行引脚分配。Vivado中通过xdc文件实现引脚配置,在文件中规定引脚的电平规范与分配对应开发板中实际的引脚,添加约束文件的方式如下图所示。点击【constrain】-》【constrs_1】右键选择add source 即可添加约束文件。引脚分配一定要对照原理图,确保该引脚空闲且满足电平规范。 Vivado的编译主要分为三步。分别为Run Synthesis(综合编译)、Run Implementation(实现编译)、Generate Bitestream(生成bit流),直接点击Generate Bitstreams会顺序执行综合编译与实现编译,生成的bit流可以利用JTEG直接烧录到板子中进行板级调试。 |

【本文地址】

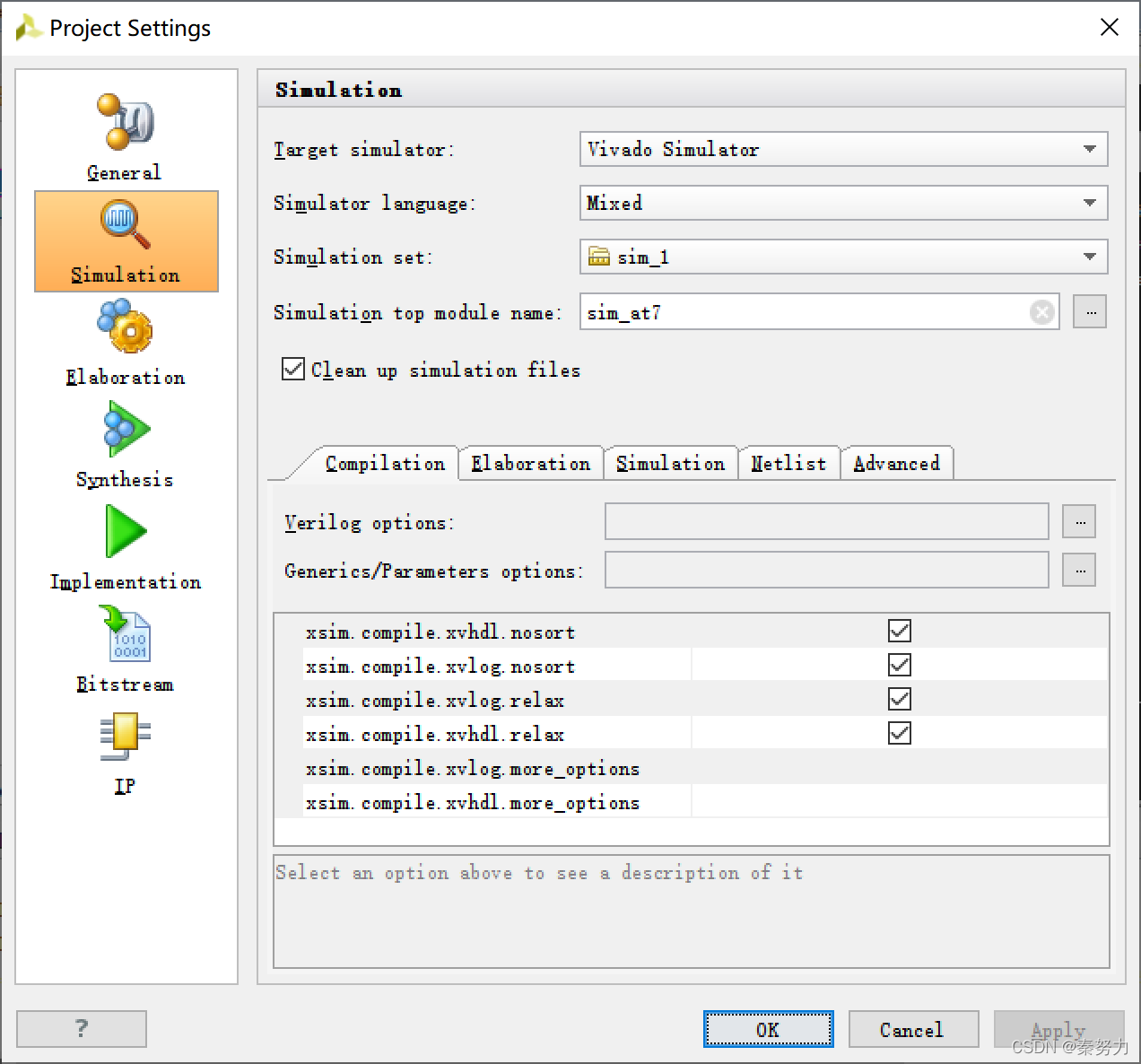

源文件和仿真文件准备好后,进行仿真设置,主要是保证仿真顶层模块名称与工程中仿真文件顶层模块名称一致。

源文件和仿真文件准备好后,进行仿真设置,主要是保证仿真顶层模块名称与工程中仿真文件顶层模块名称一致。

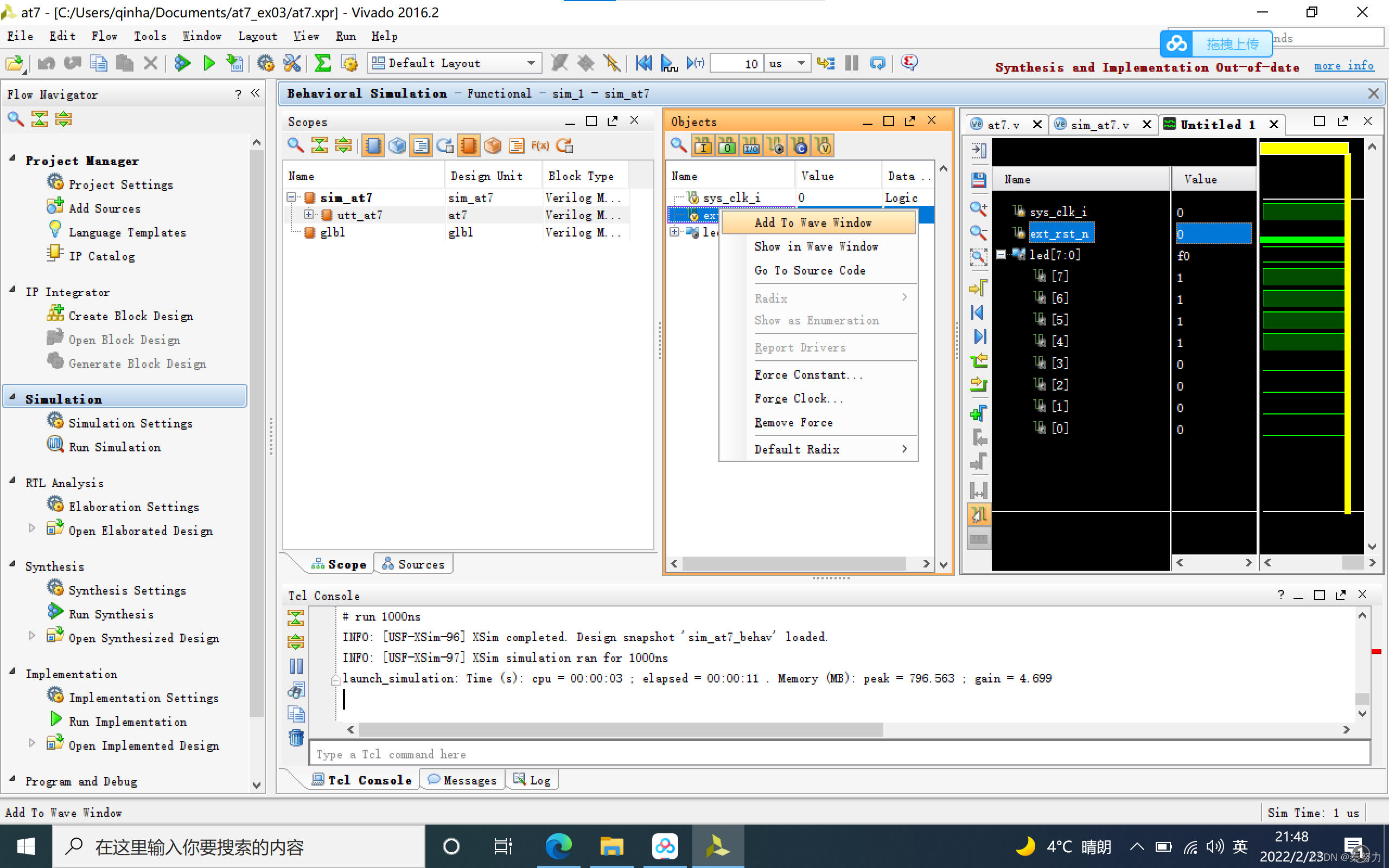

右键相应的信号,可以将波形添加到窗口,具体如图所示

右键相应的信号,可以将波形添加到窗口,具体如图所示  点击run all 进行仿真,即可查看波形。

点击run all 进行仿真,即可查看波形。

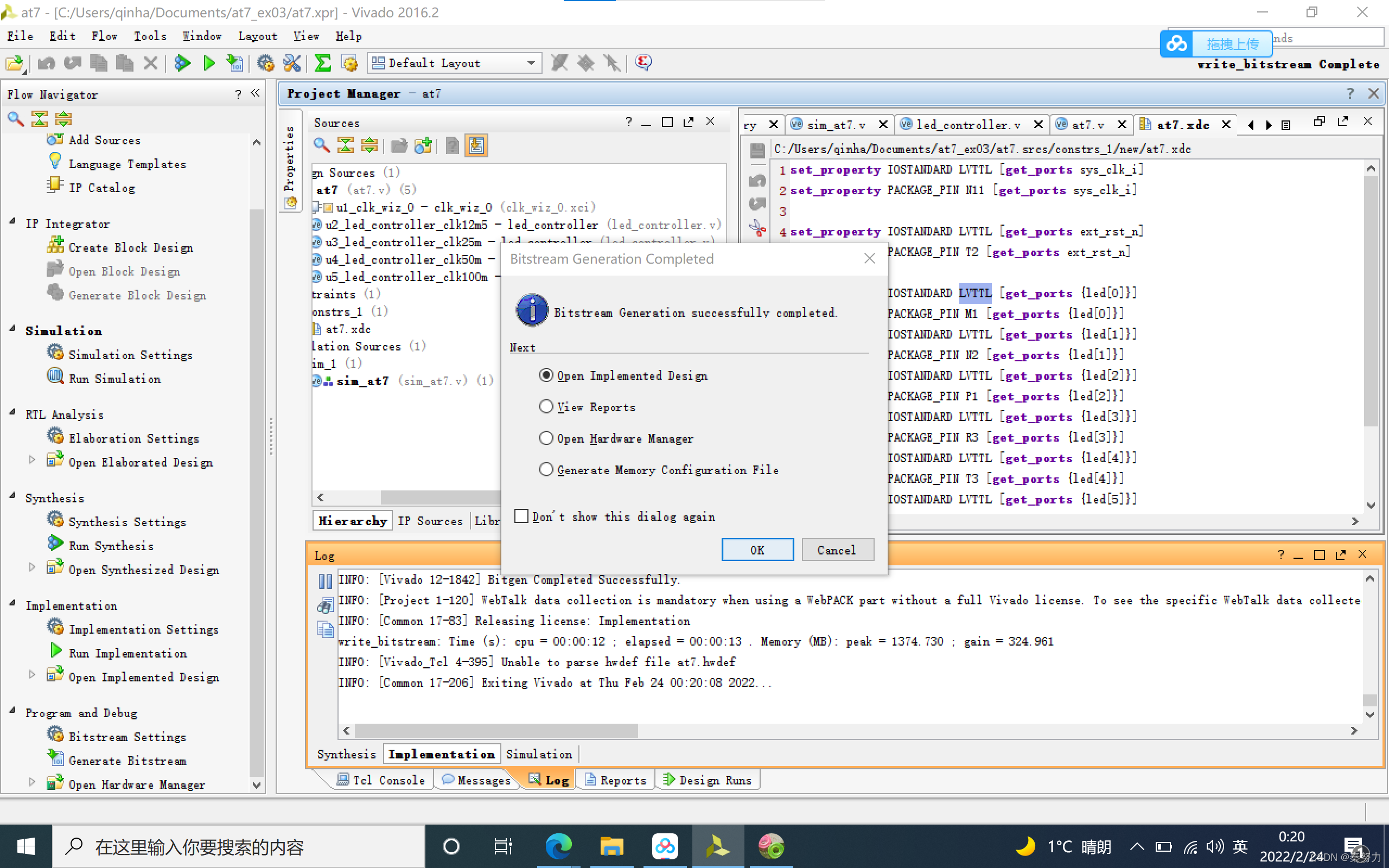

显示编译成功完成,生成bit流。

显示编译成功完成,生成bit流。