| 双向移位寄存器原理 | 您所在的位置:网站首页 › siso寄存器 › 双向移位寄存器原理 |

双向移位寄存器原理

|

触发器(FF) 是一种主要用于存储单个二进制数据位0或1的设备。但是要存储多位数据,需要多个FF。所以连接多个触发器就可以存储n位的数据。寄存器是一组串联的FF,用于存储多个数据位。存储在这些类型的寄存器中的数据可以通过移位寄存器传输。 此外,移位寄存器 (SR) 是一种数字电路,它包括一组FF,并且第一个触发器的输出引脚可任意连接到下一个FF的数据输入引脚,因为所有FF都简单地工作在相似的时钟上,然后可以将阵列位存储在寄存器中,并将移动一个位置。目前有不同类型的移位寄存器,例如SISO、SIPO、PIPO、PIPO和双向移位寄存器。本文介绍其中的一种移位寄存器——双向移位寄存器。 基本概念用于根据所选模式在右侧或左侧移位数据的寄存器称为双向移位寄存器。如果所选模式为高 (1),则数据将移至右侧;如果所选模式为低 (0),则数据将移至左侧。 其中,如果将一个二进制数(基数为2)向左移动,就是将该数乘以2,如果将同一个二进制数向右移动1位,则等于该数除以2。当然,要执行这些操作,需要一个寄存器来向任意方向移动数据。

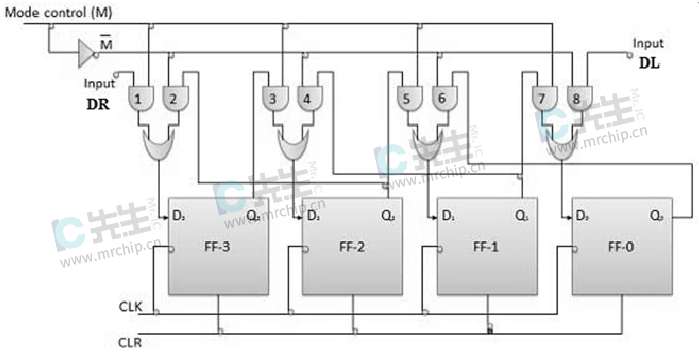

双向移位寄存器用于根据输入在右侧或左侧移位数据。该寄存器可以通过D触发器和逻辑门来实现,逻辑门允许数据位根据输入信号从一个级传输到下一个级到右侧或左侧的任何一侧。在这里,数据移位的方向由模式控制选择。

如果利用移位寄存器对数据进行乘除,则可以将二进制输入数据右移或左移,这就是所谓的双向移位寄存器。 工作原理双向移位寄存器主要包括串行右移(DR)数据输入和串行左移(DL)数据输入以及选择模式输入(M)两个串行i/ps。每当数据需要向右移动时,就会将输入提供给DR。类似地,如果数据需要在左侧移动,则输入从DL给出。 当模式控制信号为高电平时,它允许数据向右移动,而模式控制信号为低信号时,它会将数据向左移动。如果i/p数据左移1个位置,则乘以 2,如果i/p数据右移1个位置,则除以2。 真值表 双向移位寄存器在M=1和M=0两种情况下工作,这将在下面的双向移位寄存器真值表中介绍。 模式情况 操作过程 如果模式选择i/p(例如M=1),则接下来的操作是向右移动。 如果模式控制=高 (1),则启用第1、第3、第5和第7个与逻辑门,而未启用其余的第2、第4、第6和第8个与门。 串行右移数据输入 (DR) 上的二进制数据可以通过CLK脉冲应用程序上的触发器3到触发器0的一位移动到右侧位。因此对于M=1的条件,可以实现串行右移操作。 如果模式选择i/p(例如M=0),则接下来的操作是向右移动。 如果模式控制=低 (0),则启用第2、4、6和8个与门,禁用第1、3、5和7个与门。串行左移数据i/p (DL) 上的数据在CLK脉冲应用程序中从触发器0到触发器3向左移动一位。所以对于M=0的条件,可以得到串行左移操作。 Verilog代码n位双向移位寄存器的verilog代码如下所示: module shift_reg #(parameter MSB = 8) ( input d, //声明移位寄存器中第一个触发器的数据输入 i nput clk, //声明时钟的i/p到移位寄存器中的所有触发器 input en, //声明 i/p以启用打开或关闭移位寄存器 input dir , //声明i/p向右或向左移动 input rstn , //声明输入以将寄存器重置为默认值 output reg [MSB-1:0] out ; //声明o/p,读出这个寄存器中所有触发器的当前值 // 这个always块将“总是”在时钟的上升沿触发 //一旦进入block,首先会检查reset是否为0,如果是,则reset register // 如果否,则检查移位寄存器是否启用 // 如果没有=>保持之前的输出。如果是,则根据请求的方向移动 always @ (posedge clk) if (!rstn) out |

【本文地址】