| MT7621 | 您所在的位置:网站首页 › rad5807sp芯片资料 › MT7621 |

MT7621

|

项目开发需要使用MT7621,负责驱动移植,适配公司板卡。网上相关资料多为涉及openwrt的,不太符合我们裁剪要求,故记录此流程,进行深入学习研究。首先先对芯片资源做一个了解。后续计划包括uboot移植分析,kernel移植分析,rootfs构建,openwrt学习和使用,kernel驱动源码分析等。 功能框图MT7621 SoC包括一个高性能880 MHz MIPS1004Kc CPU核心和高速USB3.0/PCIe/SDXC接口,该接口旨在通过联发科(Ralink)WiFi客户端卡实现多种高性能、高性价比的IEEE 802.11n/ac应用。MT7621还有其他版本:MT7621A:双核,MT7621AT:双核四线程。在高性能、低延迟Rbus(Ralink总线)上的MT7621 SoC中有多个主机(MIPS 1004KEc、USB、PCI Express、SDXC、FE)。此外,MT7621 SoC通过低速外围总线(Pbus)支持低速外围设备,如UART-Lite、GPIO、NFI和SPI。DDR2/DDR3控制器是Rbus上唯一的总线从机。它包括一个高级内存调度器,用于仲裁来自总线主控器的请求,从而提高内存访问密集型任务的性能。

o 8-9级管道o 32位地址路径o 到缓存的64位数据路径o MIPS32增强的体系结构(版本2)功能 –标准化指令集架构 –矢量中断和对外部中断控制器的支持 –可编程异常向量库 –原子中断启用/禁用 –位字段操作说明 o MIPS16e应用程序特定扩展 –32位指令的16位编码,以提高代码密度 –专用PC相关指令,用于有效加载地址和常量 –数据类型转换说明(ZEB、SEB、ZEH、SEH) –紧凑跳跃(JRC、JALRC) –堆叠帧设置和拆除“宏”指令(保存和恢复) o MIPS MT应用程序特定扩展(ASE) –每个CORE支持2个虚拟处理单元(VPE) –每个VPE一个线程上下文(TC) o 可编程一级缓存大小 –可单独配置的指令和数据缓存 –32KB I/O缓存 –4路集合关联 –最多9个非阻塞负载 –数据缓存支持具有写分配的一致和非一致写回 –32字节缓存线大小,双字扇区-适用于标准单端口SRAM –缓存线锁定支持 –非阻塞预取 –D缓存中的重复标记阵列允许一致性请求与正常加载/存储流量并行访问缓存 o 标准内存管理单元 –每个VPE 32个双入口MIPS32样式JTLB,页面大小可变 –JTLB可在软件控制下共享 –4-5输入指令TLB –8项数据TLB o OCP总线接口单元(BIU) –32b地址和64b数据 –支持4x64b的突发 –8个条目写入缓冲区-处理逐出数据、干预响应、未缓存和未缓存加速存储数据 –简单字节启用模式允许更容易地桥接到其他总线标准 –前端L2缓存管理扩展 –干预端口支持用于1004K相干处理系统的内存一致性 o 乘除单位 –每个时钟一个32x32乘法的最大运算速率 –早期除法控制。分频时最小11个,最大34个时钟延迟 o 电源控制 –无最小频率 –支持软件控制时钟分频器 –支持广泛使用精细时钟门控 o EJTAG调试支持 –启动、停止和单步控制 –通过SDBBP指令的软件断点 –虚拟地址上的可选硬件断点;每个VPE有0、2或4条指令和0、1或2个数据断点 o SOC-it二级缓存控制器 –7级管道。(流水线存储器阵列的可选第8级。) –32位地址路径,256位内部数据路径 –8路集合关联性 –缓存大小:256KB –行大小:32字节(4个双字)

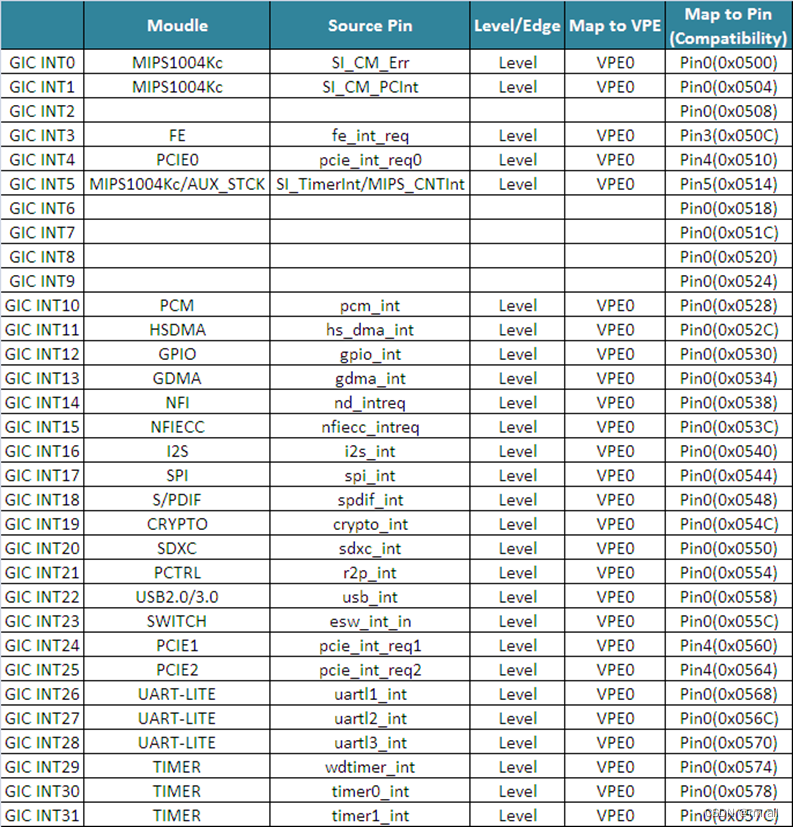

Start End Size Description 0 1BFFFFFF 448M DRAM Direct Map 1C000000 1DFFFFFF 32M 1E000000 1E0000FF 256 SYSCTL 1E000100 1E0001FF 256 TIMER 1E000200 1E0002FF 256 INTCTL 1E000300 1E0003FF 256 Flash Controller (NOR/SRAM/SDRAM) 1E000400 1E0004FF 256 Rbus Matrix CTRL 1E000500 1E0005FF 256 MIPS CNT 1E000600 1E0006FF 256 GPIO 1E000700 1E0007FF 256 S/PDIF 1E000800 1E0008FF 256 DMA_CFG_ARB 1E000900 1E0009FF 256 I2C 1E000A00 1E000AFF 256 I2S 1E000B00 1E000BFF 256 SPI CSR 1E000C00 1E000CFF 256 UARTLITE 1 1E000D00 1E000DFF 256 UARTLITE 2 1E000E00 1E000EFF 256 UARTLITE 3 1E000F00 1E000FFF 256 ANACTL 1E001000 1E0017FF 2K 1E001800 1E001FFF 2K 1E002000 1E0027FF 2K PCM (up to 16 channel) 1E002800 1E002FFF 2K Generic DMA (up to 64 channel) 1E003000 1E0037FF 2K NAND Controller *(actually 1K in Module) 1E003800 1E003FFF 2K NAND_ECC Controller *(actually 3K in module) 1E004000 1E004FFF 4K Crypto Engine 1E005000 1E005FFF 4K MEM_CTRL (DDRII/DDRIII) 1E006000 1E006FFF 4K EXT_MC_ARB 1E007000 1E007FFF 4K HS DMA 1E008000 1E00FFFF 32K 1E010000 1E0FFFFF 960K 1E100000 1E10DFFF 56K Frame Engine (FE SRAM: 0x1E108000~0x1E10DFFF) 1E10E000 1E10FFFF 8K PCIe SRAM 1E110000 1E117FFF 32K Ethernet GMAC 1E118000 1E11FFFF 32K ROM 1E120000 1E12FFFF 64K 1E130000 1E137FFF 32K SDXC 1E138000 1E13FFFF 32K 1E140000 1E17FFFF 256K PCI Express 1E180000 1E1BFFFF 256K 1E1C0000 1E1FFFFF 256K USB Host (U2+U3) 1E200000 1E23FFFF 256K 1E240000 1E24FFFF 64K 1E250000 1E7FFFFF 5824K 1E800000 1EBFFFFF 4M PCIE Direct Access for iNIC 1EC00000 1FBBFFFF 16128K 1FBC0000 1FBDFFFF 128 CM_GIC 1FBE0000 1FBEFFFF 64K 1FBF0000 1FBF7FFF 32K CM_CPC 1FBF8000 1FBFFFFF 32K CM_GCR 1FC00000 1FFFFFFF 4M ROM/SPI FLASH Direct Access 20000000 23FFFFFF 64M DRAM Re-Map 24000000 5FFFFFFF 960M 60000000 6FFFFFFF 256M PCIE Direct Access 70000000 7FFFFFFF 256M 中断

提供只读芯片修订寄存器 提供访问引导信号的窗口 支持内存重新映射配置 支持软件重置到每个平台构建块 提供寄存器以确定GPIO和其他外围引脚复用方案 为软件编程人员提供一些通电复位测试寄存器 组合各种寄存器(如时钟偏移控制、状态寄存器、备忘录寄存器等)

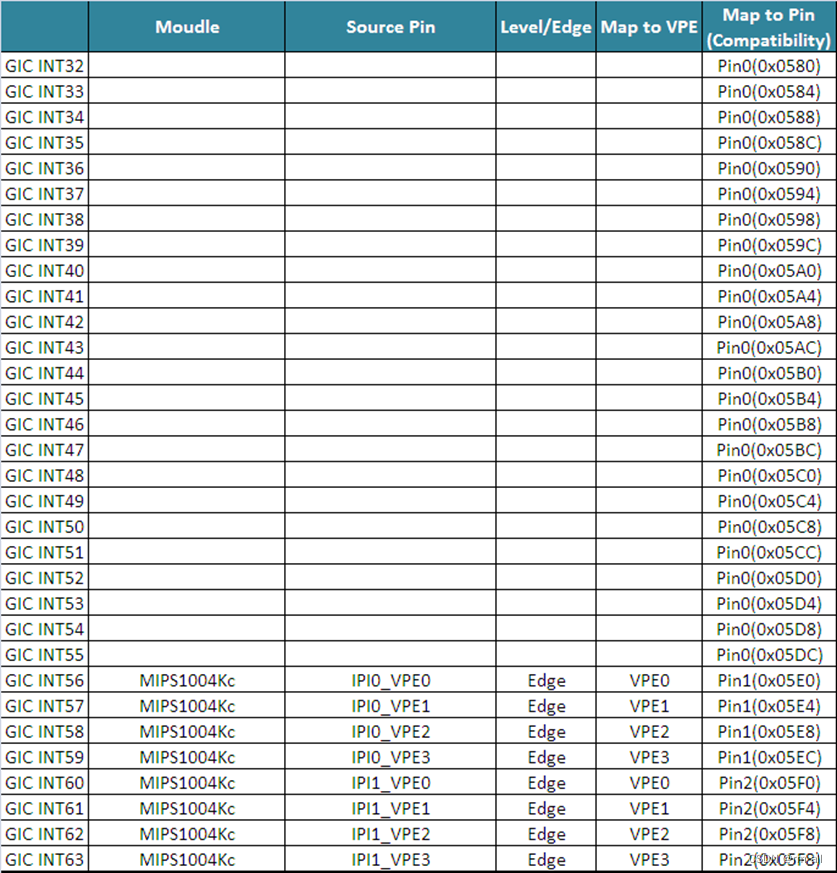

寄存器 Address Name Widt h Register Function 1E000000 CHIPID0_3 32 CHIP ID ASCII Character 0-3 1E000004 CHIPID4_7 32 CHIP ID ASCII Character 4-7 1E00000C CHIP_REV_ID 32 Chip Revision Identification 1E000010 SYSCFG 32 System Configuration Register 1E000014 SYSCFG1 32 System Configuration Register 1 1E000018 TESTSTAT 32 Firmware Test Status 1E00001C TESTSTAT2 32 Firmware Test Status 2 1E000020 BOOT_SRAM_BA SE 32 Boot from SRAM base Address 1E000024 BOOT_RELEASE 32 Release CPU's reset to let CPU boot in boot from SRAM mode 1E00002C CLKCFG0 32 Clock Configuration Register 0 1E000030 CLKCFG1 32 Clock Configuration Register 1 1E000034 RSTCTL 32 Reset Control Register 1E000038 RSTSTAT 32 Reset Status Register 1E00003C MISR_GOLDEN 32 ROM BIST MISR Golden Value 1E000040 MISR_RESULT 32 ROM BIST MISR Result Value 1E000044 CUR_CLK_STS 32 Current clock status 1E000048 PAD_UART1_GPI O0_CFG 32 PAD configuration of UART1 and GPIO0 groups 1E00004C PAD_UART3_I2C_ CFG 32 PAD configuration of UART3 and I2C groups 1E000050 PAD_UART2_JTA G_CFG 32 PAD configuration of UART2 and JTAG groups 1E000054 PAD_PERST_WDT _CFG 32 PAD configuration of PICe RST and WDT RST groups 1E000058 PAD_RGMII2_MDI O_CFG 32 PAD configuration of RGMII2 and MDIO RST groups 1E00005C PAD_SDXC_SPI_C FG 32 PAD configuration of SDXC and SPI RST groups 1E000060 GPIO_MODE 32 GPIO purpose selection 1E000068 MEMO1 32 Memory1 1E00006C MEMO2 32 Memory2 1E000070 PAD_BOPT_ESWI NT_CFG 32 PAD configuration of Bonding OPT and ESW INT groups 1E000074 PAD_RGMII1_CFG 32 PAD configuration of RGMII1 group 1E000078 CPE_ROSC_SEL0 32 1E00007C CPE_ROSC_SEL1 32 1E000080 CPU_CPE_CNT0 32 CPU CPE counter 0 1E000084 CPU_CPE_CNT1 32 CPU CPE counter 1 1E000088 CPU_CFG 32 CPU configuration 1E00008C CPU_MEM_CFG 32 CPU memory delay, power down and sleep control 1E000090 FMTR_CFG0 32 Frequency meter configuration 0 1E000094 FMTR_CNT_MAX 32 Frequency meter count maximum 1E000098 FMTR_CNT_MIN 32 Frequency meter count minimum 1E00009C FMTR_CNT_VAL 32 Frequency meter counter value 重要位: SYSCFG:XTAL模式选择、DDR类型选择 SYSCFG1:Gigabit Port #1 mode选择、Gigabit Port #2 mode选择、Pcie mode选择 CLKCFG0:CPU时钟选择、分频、PCIE时钟源、外设时钟等 CLKCFG1:SDHC、AUX、PCIE0,1,2、ETH、UART1,2,3、SPI、I2C、I2S、NAND、GDMA等外设时钟控制 RSTCTL:上述模块及系统复位控制 PAD_UART1_GPIO0_CFG:串口1的GPIO电气属性配置 GPIO_MODE:部分IO的功能复用配置 定时器Timero 每个定时器都有独立的时钟。o 每个定时器的独立中断。o 两个通用定时器和一个看门狗定时器。看门狗计时器在超时时重置系统。o 定时器模式 --周期模式(倒计数模式,会重装载) 在周期模式下,计时器从限制值倒计时至零。当计数为零时,会生成中断。达到零后,将限制值重新加载到计时器中,计时器再次倒计时。有限的零值禁用计时器。 --超时模式(倒计数模式,不会重装载) 在超时模式下,计时器从限制值倒计时至零。当计数为零时,会生成中断。在此模式下,当计时器达到零时,ENABLE位被重置,停止计数器。 --看门狗模式 在看门狗模式下,计时器从限制值倒计时至零。如果在计数为零之前未重新加载负载值或未禁用计时器,则芯片将复位。当这种情况发生时,芯片中的每个寄存器都被复位,除了系统控制块中RSTSTAT寄存器中的看门狗复位状态位WDRST;当它重新执行引导程序时,它保持设置为提醒固件超时事件。

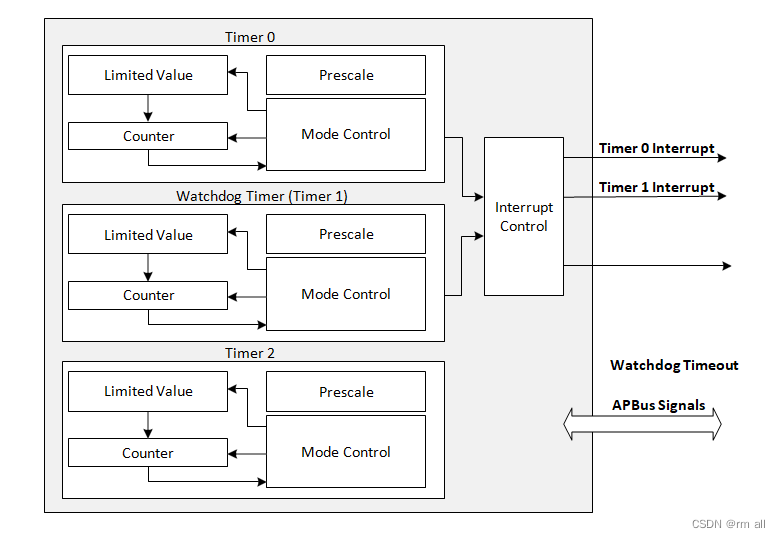

寄存器 Address Name Widt h Register Function 1E000100 TGLB_REG 32 RISC Global Control Register 1E000110 T0CTL_REG 32 RISC Timer 0 Control Register 1E000114 T0LMT_REG 32 RISC Timer 0 Limit Register 1E000118 T0_REG 32 RISC Timer 0 Register 1E000120 WDTCTL_REG 32 Watch Dog Timer Control Register 1E000124 WDTLMT_REG 32 Watch Dog Timer Limit Register 1E000128 WDT_REG 32 Watch Dog Timer Register 1E000130 T1CTL_REG 32 RISC Timer 1 Control Register 1E000134 T1LMT_REG 32 RISC Timer 1 Limit Register 1E000138 T1_REG 32 RISC Timer 1 Register 系统计时计数器Address Name Width Register Function 1E000500 STCK_CNT_CFG 32 MIPS Configuration 1E000504 CMP_CNT 32 MIPS Compare Sets the cutoff point for the free run counter (MIPS counter). If the free run counter equals the compare counter, then the timer circuit generates an interrupt. The interrupt remains active until the compare counter is written again. 1E000508 CNT 32 MIPS Counter The MIPS counter (free run counter) increases by 1 every 20 us (50 KHz). The counter continues to count until it reaches the value loaded into CMP_CNT. 串口(UART Lite)2针UART 16550兼容寄存器集,除数锁存寄存器除外 5-8个数据位 1-2个停止位(5个数据位支持1或2个停止位) 偶数、奇数、粘连或无奇偶校验 所有标准波特率高达345600 b/s 16字节接收缓冲器 16字节传输缓冲器 接收缓冲区阈值中断 传输缓冲区阈值中断 异步模式下的错误起始位检测 内部诊断功能 中断模拟 用于通信链路故障隔离的环回控制 寄存器描述见手册 可编程I/O独立输入、输出和输入输出的参数化数量 每个引脚的独立极性控制 任何输入转换上的独立屏蔽边缘检测中断

I/O表 PAD Name Function 0 Function 1 Function 2 Function 3 strap pmux_group GPIO PAD_GPIO0 gpio (I/O) 0 gpio_psel[0] 0 PAD_RXD1 rxd1 (I) gpio (I/O) uartl_psel[0] 1 PAD_TXD1 txd1 (O) gpio (I/O) 1 2 PAD_I2C_SD i2c_sd (I/O) gpio (I/O) i2c_psel[0] 3 PAD_I2C_SCLK i2c_sclk (I/O) gpio (I/O) 4 PAD_RTS3_N rts3_n (O) gpio (I/O) i2s_sdo (O) spdif_tx (O) 2 uart3_psel[1:0] 5 PAD_CTS3_N cts3_n (I) gpio (I/O) i2s_clk (I/O) gpio (I/O) 6 PAD_TXD3 txd3 (O) gpio (I/O) i2s_ws (I/O) gpio (I/O) 7 PAD_RXD3 rxd3 (I) gpio (I/O) i2s_sdi (I) gpio (I/O) 8 PAD_RTS2_N rts2_n (O) gpio (I/O) pcm_dtx (I/O) gpio (I/O) 3 uart2_psel[1:0] 9 PAD_CTS2_N cts2_n (I) gpio (I/O) pcm_drx (I) gpio (I/O) 10 PAD_TXD2 txd2 (O) gpio (I/O) pcm_clk (O) spdif_tx (O) 4 11 PAD_RXD2 rxd2 (I) gpio (I/O) pcm_fs (I/O) gpio (I/O) 12 PAD_JTDO jtdo (I/O) gpio (I/O) jtag_psel[0] 13 PAD_JTDI jtdi (I) gpio (I/O) 14 PAD_JTMS jtms (I) gpio (I/O) 15 PAD_JTCLK jtclk (I) gpio (I/O) 16 PAD_JTRST_N jtrst_n (I) gpio (I/O) 17 PAD_WDT_RST_N wdt_rst_n (I/O) gpio (I/O) ref_clk0_out (O) wdt_psel[1:0] 18 PAD_PERST_N perst_n (O) gpio (I/O) ref_clk0_out (O) 5 perst_psel[1:0] 19 PAD_MDIO mdio (I/O) gpio (I/O) gpio (I/O) mdio_psel[1:0] 20 PAD_MDC mdc (O) gpio (I/O) ref_clk0_out (O) 6 21 PAD_G1_TXD0 g1_txd[0] (I/O) gpio (I/O) rgmii1_psel[0] 49 PAD_G1_TXD1 g1_txd[1] (I/O) gpio (I/O) 50 PAD_G1_TXD2 g1_txd[2] (I/O) gpio (I/O) 51 PAD_G1_TXD3 g1_txd[3] (I/O) gpio (I/O) 52 PAD_G1_TXEN g1_txen (I/O) gpio (I/O) 53 PAD_G1_TXC g1_txc (I/O) gpio (I/O) 54 PAD_G1_RXD0 g1_rxd[0] (I/O) gpio (I/O) 55 PAD_G1_RXD1 g1_rxd[1] (I/O) gpio (I/O) 56 PAD_G1_RXD2 g1_rxd[2] (I/O) gpio (I/O) 57 PAD_G1_RXD3 g1_rxd[3] (I/O) gpio (I/O) 58 PAD_G1_RXDV g1_rxdv (I/O) gpio (I/O) 59 PAD_G1_RXC g1_rxc (I/O) gpio (I/O) 60 PAD_G2_TXD0 g2_txd[0] (I/O) gpio (I/O) rgmii2_psel[0] 22 PAD_G2_TXD1 g2_txd[1] (I/O) gpio (I/O) 23 PAD_G2_TXD2 g2_txd[2] (I/O) gpio (I/O) 24 PAD_G2_TXD3 g2_txd[3] (I/O) gpio (I/O) 25 PAD_G2_TXEN g2_txen (I/O) gpio (I/O) 26 PAD_G2_TXC g2_txc (I/O) gpio (I/O) 27 PAD_G2_RXD0 g2_rxd[0] (I/O) gpio (I/O) 28 PAD_G2_RXD1 g2_rxd[1] (I/O) gpio (I/O) 29 PAD_G2_RXD2 g2_rxd[2] (I/O) gpio (I/O) 30 PAD_G2_RXD3 g2_rxd[3] (I/O) gpio (I/O) 31 PAD_G2_RXDV g2_rxdv (I/O) gpio (I/O) 32 PAD_G2_RXC g2_rxc (I/O) gpio (I/O) 33 PAD_SPI_CS0_N spi_cs0 (I/O) gpio (I/O) nd_cs_n (O) 7 spi_psel[1:0] 34 PAD_SPI_CS1_N spi_cs1 (I/O) gpio (I/O) nd_we_n (O) 8 35 PAD_SPI_SCLK spi_clk (I/O) gpio (I/O) nd_re_n (O) 9 36 PAD_SPI_MISO spi_miso (I/O) gpio (I/O) nd_d[4] (I/O) 37 PAD_SPI_MOSI spi_mosi (I/O) gpio (I/O) nd_d[5] (I/O) 38 PAD_SPI_WP_N spi_wp (I/O) gpio (I/O) nd_d[6] (I/O) 39 PAD_SPI_HOLD_N spi_hold (I/O) gpio (I/O) nd_d[7] (I/O) 40 PAD_SD_WP sd_wp (I) gpio (I/O) nd_wp (O) sd_psel[1:0] 41 PAD_SD_CLK sd_clk (I/O) gpio (I/O) nd_rb_n (I) 42 PAD_SD_CD sd_cd (I) gpio (I/O) nd_cle (O) 43 PAD_SD_CMD sd_cmd (I/O) gpio (I/O) nd_ale (O) 44 PAD_SD_D0 sd_data[0] (I/O) gpio (I/O) nd_d[0] (I/O) 45 PAD_SD_D1 sd_data[1] (I/O) gpio (I/O) nd_d[1] (I/O) 46 PAD_SD_D2 sd_data[2] (I/O) gpio (I/O) nd_d[2] (I/O) 47 PAD_SD_D3 sd_data[3] (I/O) gpio (I/O) nd_d[3] (I/O) 48 PAD_ESW_INT esw_int(I) gpio (I/O) esw_psel[0] 61 寄存器列表 These registers are used to enable the condition of rising edge triggered interrupt. 1E000654 GINT_REDGE_1 32 GPIO32 to GPIO63 rising edge interrupt enable register These registers are used to enable the condition of rising edge triggered interrupt. 1E000658 GINT_REDGE_2 32 GPIO64 to GPIO95 rising edge interrupt enable register These registers are used to enable the condition of rising edge triggered interrupt. 1E000660 GINT_FEDGE_0 32 GPIO0 to GPIO31 falling edge interrupt enable register These registers are used to enable the condition of falling edge triggered interrupt. 1E000664 GINT_FEDGE_1 32 GPIO32 to GPIO63 falling edge interrupt enable register These registers are used to enable the condition for falling edge triggered interrupt. 1E000668 GINT_FEDGE_2 32 GPIO64 to GPIO95 falling edge interrupt enable register These registers are used to enable the condition of falling edge triggered interrupt. 1E000670 GINT_HLVL_0 32 GPIO0 to GPIO31 high level interrupt enable register These registers are used to enable the condition of high level triggered interrupt. The bit in this register and the corresponded bit in GINT_LLVL_0 cannot be set to 1 at the same time. 1E000674 GINT_HLVL_1 32 GPIO32 to GPIO63 high level interrupt enable register These registers are used to enable the condition of high level triggered interrupt. The bit in this register and the corresponded bit in GINT_LLVL_1 cannot be set to 1 at the same time. 1E000678 GINT_HLVL_2 32 GPIO64 to GPIO95 high level interrupt enable register These registers are used to enable the condition of high level triggered interrupt. The bit in this register and the corresponded bit in GINT_LLVL_2 cannot be set to 1 at the same time. 1E000680 GINT_LLVL_0 32 GPIO0 to GPIO31 low level interrupt enable register These registers are used to enable the condition of low level triggered interrupt. The bit in this register and the corresponded bit in GINT_HLVL_0 cannot be set to 1 at the same time. 1E000684 GINT_LLVL_1 32 GPIO32 to GPIO63 low level interrupt enable register These registers are used to enable the condition of low level triggered interrupt. The bit in this register and the corresponded bit in GINT_HLVL_1 cannot be set to 1 at the same time. 1E000688 GINT_LLVL_2 32 GPIO64 to GPIO95 low level interrupt enable register These registers are used to enable the condition of low level triggered interrupt. The bit in this register and the corresponded bit in GINT_HLVL_2 cannot be set to 1 at the same time. 1E000690 GINT_STAT_0 32 GPIO0 to GPIO31 interrupt status register These registers are used to record the GPIO current interrupt status. 1E000694 GINT_STAT_1 32 GPIO32 to GPIO63 interrupt status register These registers are used to record the GPIO current interrupt status. 1E000698 GINT_STAT_2 32 GPIO64 to GPIO95 interrupt status register These registers are used to record the GPIO current interrupt status. 1E0006A0 GINT_EDGE_0 32 GPIO0 to GPIO31 edge status register These registers are used to record the GPIO current interrupt's edge status. These registers are useful only in edge triggered interrupt. 1E0006A4 GINT_EDGE_1 32 GPIO32 to GPIO63 edge status register These registers are used to record the GPIO current interrupt's edge status. These registers are useful only in edge triggered interrupt. 1E0006A8 GINT_EDGE_2 32 GPIO64 to GPIO95 edge status register These registers are used to record the GPIO current interrupt's edge status. These registers are useful only in edge triggered interrupt. I2C控制器可编程I2C总线时钟速率 支持同步集成电路间(I2C)串行协议 双向数据传输 可编程地址宽度高达8位 顺序字节读写能力 可传输设备地址和数据地址,用于设备、页面和地址选择 支持标准模式和快速模式 寄存器 Address Name Widt h Register Function 1E000908 SM0CFG0 32 SERIAL INTERFACE MASTER 0 CONFIG 0 REGISTER 1E000910 SM0DOUT 32 SERIAL INTERFACE MASTER 0 DATAOUT REGISTER 1E000914 SM0DIN 32 SERIAL INTERFACE MASTER 0 DATAIN REGISTER 1E000918 SM0ST 32 SERIAL INTERFACE MASTER 0 STATUS REGISTER 1E00091C SM0AUTO 32 SERIAL INTERFACE MASTER 0 AUTO-MODE REGISTER 1E000920 SM0CFG1 32 SERIAL INTERFACE MASTER 0 CONFIG 1 REGISTER 1E000928 SM0CFG2 32 SERIAL INTERFACE MASTER 0 CONFIG 2 REGISTER 1E000940 SM0CTL0 32 Serial interface master 0 control 0 register 1E000944 SM0CTL1 32 Serial interface master 0 control 1 register 1E000950 SM0D0 32 Serial interface master 0 data 0 register 1E000954 SM0D1 32 Serial interface master 0 data 1 register 1E00095C PINTEN 32 Peripheral interrupt enable register 1E000960 PINTST 32 Peripheral interrupt status register 1E000964 PINTCL 32 Peripheral interrupt clear register NAND Flash 接口控制器能够进行4/6/8纠错的ECC(BCH码)加速。(带ECC引擎) 可编程页面大小和备用大小 可编程FDM数据大小和受保护的FDM数据尺寸。 通过APB总线进行字/字节访问。 用于大规模数据传输的DMA。 锁存敏感中断,用于指示读取、编程和擦除操作的就绪状态。 可编程等待状态、命令/地址设置和保持时间、读取启用保持时间和写入启用恢复时间。 寄存器列表见手册 NFI ECC ControllerECC(BCH码)加速能够在一个完整的或小于8192( |

【本文地址】