| 【电子器件检验标准】JEDEC | 您所在的位置:网站首页 › jetec标准 › 【电子器件检验标准】JEDEC |

【电子器件检验标准】JEDEC

|

摘要:目前,最新的JS-002标准为2018年版,涵盖的内容包括标准的使用范围、试验目的、试验过程、实验方法和相关注意点。本文主要论述关于JS-002-2018的部分基础内容,包括标准的产生、应用的器件和试验过程的注意事项。 正文: 1. 标准的产生 JS-002-2018中文译名为《用于静电放电的敏感度测试-带电器件模式(CDM)》,由JEDEC和ESDA联合编写,取代了JEDEC之前的JESD22-C101和ANSI/ESD S5.3.1。 CDM是Charged Device Model的首字母缩写,JS-002-2018中对CDM模型给出解释:器件本身带电(例如,器件表面的摩擦起电或者通过电场感应),并在接触导电物体时迅速放电,放电时间仅有几纳秒。CDM是一种金属-金属放电,通过空气击穿电弧产生产生非常快速的电荷转移,达到数十安培的峰值电流。CDM放电模式很难标准量化和再现,在CDM模型中,观察到的MOS器件典型失效机制是介电损伤。 2. 应用的器件 JS-002-2018应用的器件如表1所示,需要注意的是插接式放电模型测试仪不适用JS-002-2018。图1~图5是各种器件的示意图。 表1 JS-002-2018应用的器件 应用的器件器件特点半导体器件以MOS晶体管为主,成本低,应用最广。表面声波(SAW)器件 SAW:surface acoustic wave 广泛地用于工业和军事装备中。它体积小、结构牢固、频段宽,而且能大批生产。光电器件一种将电能转换成光能的器件。它包括发光二极管、发光数字管等。混合集成电路混合集成电路具有组装密度大、可靠性高、电性能好等特点。相对于单片集成电路,它设计灵活,工艺方便,便于多品种小批量生产;并且元件参数范围宽、精度高、稳定性好,可以承受较高电压和较大功率。多芯片模块实现电子整机小型化、多功能化、高性能和高可靠性。

图1 MOS管

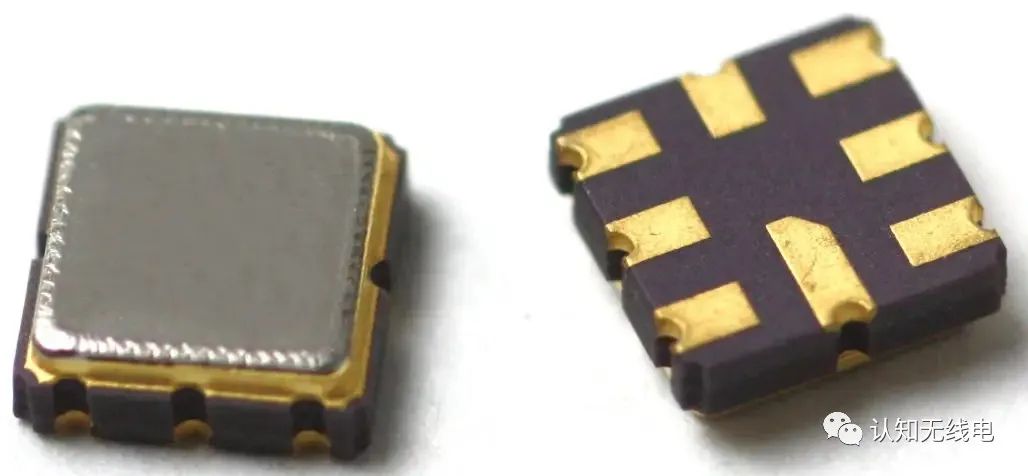

图2 表面声波(SAW)器件

图3 光电器件

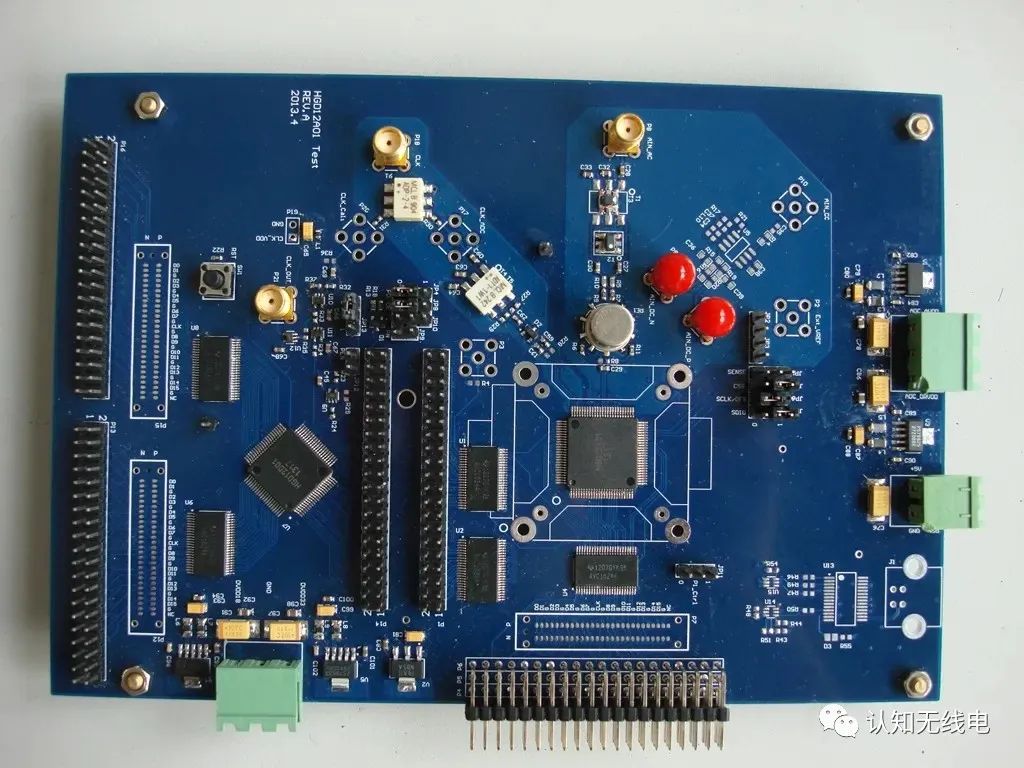

图4 混合集成电路

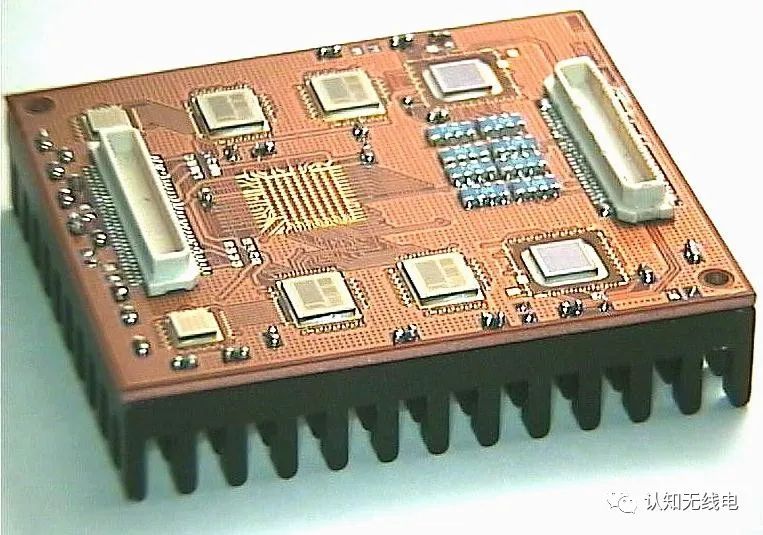

图5 多芯片模块 3. 试验过程的注意事项 CDM是破坏性试验,试验全过程需要进行防静电措施。试验环境可以使用浓度不小于70%的异丙醇进行清洁。测试机台如图6所示。

图6 CDM测试机台(Orion型) Orion2机型的使用指南可参照Orion2 CDM 操作系统-操作部分20211207 CDM测试机台中的关键部件是探针,是探测带电器件放电的关键,如图6所示。根据JS-002-2018,探针试验时的湿度不应大于30% RH,这是由于湿度越低,探测的放电过程越明显。CDM的试验温度应为室温。器件每个引脚或锡球,至少需要进行1次正极放电和1次负极放电,两次放电的时间应该足够长。较长的放电间隔不会导致器件的过分充电,只会增加试验时间。 在进行CDM后,应对器件进行静态测试和动态测试。如果测试的参数与委托方的参考数据表中的数据不一致,应认为失效。如果证明失效不是由于CDM引起的,可以排除失效。 需要说明的是,静态测试的方法主要是引脚漏电和检测待机电流等,静态测试不能直接说明器件失效,但可以作为辅助说明验证器件失效。 如果需要补充测试,可以在依次按照低温(-40℃)、常温(25℃)和高温(85℃)进行测试。 总结:CDM是一种常见的ESD试验,随着电子器件技术水平的上升,检验过程中的CDM试验变得尤为重要。 参考文献: [1] 表1中的“器件应用场景”参照百度词条进行整理。 [2] 图1~图6图片来自百度图片进行整理。 |

【本文地址】