| 书接上回PLL1可行方案试行 | 您所在的位置:网站首页 › PLL带宽影响 › 书接上回PLL1可行方案试行 |

书接上回PLL1可行方案试行

|

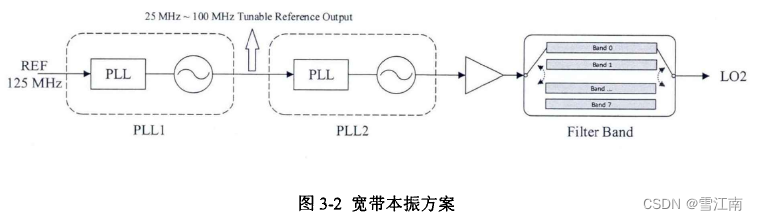

锁相环低杂散快锁定优相噪猜想之进阶版_雪江南的博客-CSDN博客 [便携式频谱分析仪射频前端的研究和设计 __by王想] 本振模块设计方案 如图3-2所示,该本振方案采用125MHz参考输入,用一片集成VCO的宽带锁相环芯片化L1输出25M~100M化的可变参考信号。PLL1的输出作为PLL2的参考,最终产生600MHz~6GHz的宽带本振信号。该方案牺牲相位噪声为代价达到降低杂散的效果。 PLL2输出的宽带本振信号功率在输出频率为2000MHz时-2dBm,在输出频率为6000MHz时-7dBm,不满足系统中L02对功率的要求,因此,在PLL2信号输出端级 联一个宽带放大器。 锁相环直接输出的本振信号含有较高的二次谐波、H次谐波及二分之一谐波分量,谐波功率较高时,会将该谐波附近的射频信号解调至中频频带上,从而造成频谱分析仪巧慢结果中出现"虚假姻谱信息。因此,在放大器输出端将600MHz~6G化的信号通过滤波器组进行滤波,从而获得纯净的本振信号。

PLL2是宽带小数分频锁相环芯片,内部集成了基带输出为1.5GHz-3.0GHz的低噪声压控振荡器。片内通过分频及倍频设置保证了输出频率覆盖600MHz至6GHz,具有15dBc的H次谐波抑制度,鉴相器鉴相频率最高能够达到100MHz,因此,用户可W根据系统设计需要拓宽PLL的环路带宽。此外,它还包含有从OdB到9dB(3dB步进)的射频输出功率控制,可获得更平坦的输出功率。论文中将600Mhz~3000Mhz 频带内增益值设置为OdB,将3000MHz-4500MHz频带内输出增益设置为3dB,将4500MHz-6000MHz频带内输出增益设置为6dB,从而达到整个输出频带内输出信号增益平坦的目的,使解调器王作在最佳性能。由于PLL2输出的谐波抑制度最差时为10dBc,不满足系统对本振信号的设计要求,方案设计中在信号源的最末级级联滤波器组,从而达到増加谐波抑制度目的。 1. 本振杂散抑制方案 1.1 杂散的来源 整数边界杂散 整数边界杂散发生在PFD频率的整数倍处,并且在接近载波频率时最强。如果可以改变PFD频率,使PFD频率的整数倍与载波频率的偏移量足够大,那么IBS功率将降低到一个没有问题的水平。 在整数频率综合器中,压控振荡器通常工作在鉴相器鉴相频率的整数倍上,这种条件下通常会产生杂散信号。从频谱上看,这些不被期望的杂散信号极为接近载波频率,因此通常被简单地归类于参考参考边带频率。由于电路的隔离能力有限,参考信号的谐波同样会出现在载波频率的远端。与参考频率无关的杂散信号必然来源于外界噪声源。外界杂散能够通过供电、地平面、输出端或由环路滤波器隔离有限而间接地与VCO输出频率发生调制效应,它们同样能够直接賴合到射频输出端。参考源杂散电平通常低于-100化C,低噪声电源用电将会降低外界杂散干扰。 小数边界杂散 与整数频率综合器不同,小数频率综合器的杂散信号产生时VCO的工作频率和鉴 相器鉴相频率的整数倍频率无直接关系,它是由VCO和鉴相器谐波的互相调制产生的。 因此,当VCO工作频率在鉴相频率的整数倍附近时,杂散泄露将増强;当VCO工作频率和鉴相频率的整数倍相同时,此时为整数边界杂散。 假设鉴相器的鉴相频率为fpD,VCO的工作频率为fvco,VCO工作频率与距离它最近的参考谐波频率之间的间隔为A,那么小数边界杂散较强时,满足下列关系:

式中,n、d、m均为正整数且满足d<m。nfpd。称为整数倍部分,称为小数倍部分。m指杂散产物的阶数,m越大,对应的杂散越小,通常m>4时杂散可以忽略不计。当△小于环路滤波器的滤波带宽时,输出信号可能表现出较强的小数边界杂散。d=0条件下杂散最强,此时VCO工作频率和鉴相频率的整数倍之间的频率差小于环路带宽,可称之为"带内整数边界"情况。 1.2 杂散抑制算法 宽带PLL芯片采用小数分频模式,杂散抑制算法的目的就是通过改变鉴相器的鉴相频率,从而相应地改变N的整数部分和小数部分,达到将可能出现的杂散信号转移到环路滤波器带宽么外的目的。PLL系统中有两种方式可以实现该目的:一是使用可编程的参考源,即参考频率可控;二是改变参考信号分频比。

如图3-3和图3-4所示,当小数边界杂散位于环路滤波器滤波带宽之内时,相位噪声上体现出的杂散大小为-55dBc,通过改变鉴相器鉴相频率,N的整数部分和小数部分重新调整之后,相位噪声图上杂散大小为-97dBc。 论文中用PLL1作为可变参考源,输出25MHz-100MHz的可调参考信号,因此, 将PLL2的参考分频比R设置为1。实验发现,Nfrae满足〇.〇5<Nftac<0.15时,小数分频锁相环的杂散大小优于-100dBc。杂散抑制算法具体的实现过程如下: (1).根据输出频率确定分频因子Div和倍频因子Dou,从而得到VC0的基准频率 Fvco。论文使用的宽带PLL2内部集成VCO的工作带宽为1.5~3.0GHz。可根据Fvco=frf*Div/Dou计算得到VCO工作频点。 (2).根据fvco的值和当前的fpD,计算出当前的Nint和Nfrac。 (3).判断Wfrae是否满足0.05<Nfrace<0.15,若不满足,则调整参考源的频率,重复.上述过程,直到满足该条件为止。 (4).使用满足条件的和配置频率综合器,得到输出信号。 本振输出信号频率范围是600MHz~6000MHz,不同的输出频点下,鉴相频率可能不同,因此,需要根据鉴相器鉴相频率的具体值调整芯片内部的电荷亲电流,从而补偿鉴相器鉴相频率改变对环路特性的影响。通常,电荷累电流随鉴相频率的增加而减小。

上图所示的是固定参考信号和可变参考信号下的输出信号杂散情况。固定鉴相频率为60MHz时,在鉴相频率的整数倍边界处杂散达到最大值;在鉴相频率的m阶边界处杂散较强。可变鉴相频率时,通过调整N值,可得到相同频率的输出信号,与固定鉴相频率不同的是,输出信号的杂散处于环路带宽之外,因此,杂散得到很好的抑制。然而,当鉴相频率的可选值为确定的n个值时,n越小,个别频点处杂散抑制效果越差。

|

【本文地址】

鉴相频率改变时,相应地改变电荷累电流可保证环路滤波器环路特性的稳定。

鉴相频率改变时,相应地改变电荷累电流可保证环路滤波器环路特性的稳定。