| 【Cache篇】Cache的分类 | 您所在的位置:网站首页 › Cache篇初见Cache › 【Cache篇】Cache的分类 |

【Cache篇】Cache的分类

|

🌟🌟🌟博主主页:MuggleZero 🌟🌟🌟

《ARMv8架构初学者笔记》专栏地址:《ARMv8架构初学者笔记》

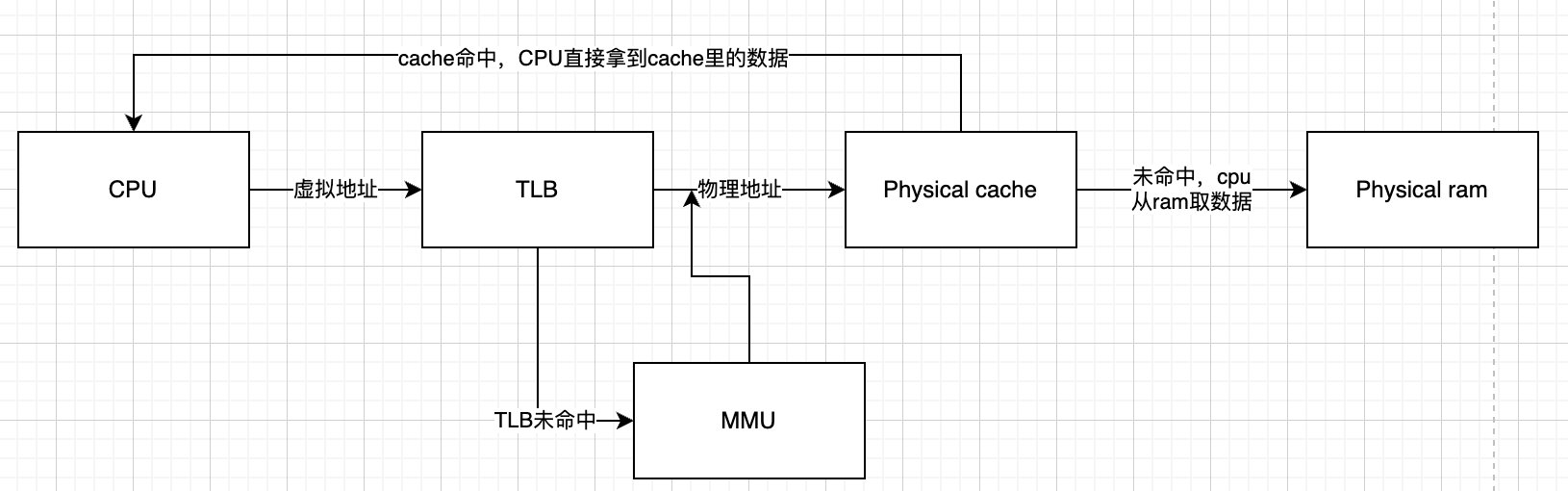

前文: 【Cache篇】初见Cache 【Cache篇】Cache的映射方式 【Cache篇】包容性和排他性的Cache CPU在访问存储器时,访问的地址是虚拟地址(VA, virtual address),在经过TLB和MMU的映射后变成了物理地址(Physical address,PA)。 TLB只能用于加速虚拟地址到物理地址的转换。在得到物理地址后,如果每次都从内存中取数据,效率会很低。因此现代处理器设计了多级cache来加速数据访问,然而在查询cache时使用虚拟地址还是物理地址呢?首先我们要搞清楚物理高速缓存和虚拟高速缓存。 物理高速缓存什么是物理高速缓存?得到物理地址后,使用物理地址查询高速缓存。缺点是CPU只有在查询TLB和MMU后才能访问cache,流水线时间延迟时间相对来说增加了。

什么是虚拟高速缓存?使用虚拟地址进行寻址cache,无需访问TLB和MMU。

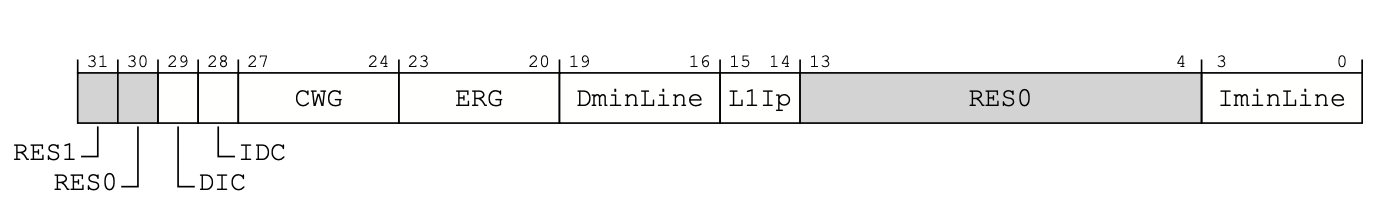

但是虚拟高速缓存会导致重名和同名问题。 重名问题重名问题是多个虚拟地址映射到同一个物理地址引发的。 同名问题同名问题是一个虚拟地址可能由于进程切换等原因映射到不同物理地址而引发的问题。 Cache类型在CPU设计的时候就已经确定了是通过虚拟地址寻址cache,还是物理地址寻址cache。Cache有以下四种,VIVT、AIVIVT、VIPT、PIPT和VPIPT。 VIVTVIVT使用虚拟地址的索引域和虚拟地址的标记域,相当于虚拟高速缓存。 早期的ARM9采用VIVT寻址方式,无须经过MMU的翻译,就可以直接使用虚拟地址的Index和Tag来查找Cache Line,这种方式会导致严重的重名问题。 AIVIVTAIVIVT是具有ASID标记的VIVT。 VIPTVIPT使用虚拟地址的索引域和物理地址的标记域。 ARM11系列处理器采用VIPT方式,虚拟地址会同时被送到MMU/TLB中翻译,以及cache中寻址。在MMU/TLB中,VPN被翻译成了PFN,与此同时,使用虚拟地址的Index和offset来查询cache组。当MMU完成地址翻译后,再使用物理地址的Tag来匹配Cache Line。 缺点是可能会导致重名问题,当使用虚拟地址的Index和offset来查询cache组时,可能会导致多个Cache Set被映射到同一个物理地址。 IVIPT是VIPT在指令cache中应用 PIPTPIPT使用物理地址的索引域和物理地址的标记域,相当于物理高速缓存。 Cortex-A系列开始采用PIPT的cache寻址方式,不会导致重名问题,cache中只有一个cache set与之对应,但是加大了芯片设计复杂度。 VPIPTVPIPT是能感知VMID的PIPT。 CTR, Cache Type Register寄存器的L1Ip表示实现的cache类型:

对于一个VPIPT指令缓存。 如果VMID被用于当前的安全状态,那么从EL1和EL0获取的指令只有在使用指令缓存中的条目被获取时使用的VMID时才允许在缓存中命中。 如果VMID被用于当前安全状态,在EL0或EL1执行的指令缓存维护指令,只有当这些条目是使用缓存维护指令执行时的VMID获取的,才要求对指令缓存中的条目产生影响。 欢迎关注我的个人微信公众号,一起交流学习嵌入式开发知识! 关注「求密勒实验室」 |

【本文地址】