| FPGA图像处理 | 您所在的位置:网站首页 › 720p图像大小 › FPGA图像处理 |

FPGA图像处理

|

摘要

本文利用zynq7020芯片实现了cameralink接口时序控制,将自制的测试采图上传至PC端上位机进行显示。其中,图片格式为1280@720P大小的的RGB888彩色图条。旨在进一步理解cameralink协议的传输规则,以及探究协议的实现方式。此外也起到了对现有采集卡及软件的测试调试作用。这些都为下一阶段图像处理的学习及对工业相机的研究打下基础。 1 理论基础 1.1 cameralink协议camearlink协议手册涉及内容很多,包括不同的工作模式,此次用的是base模式。在这里简要做总结。

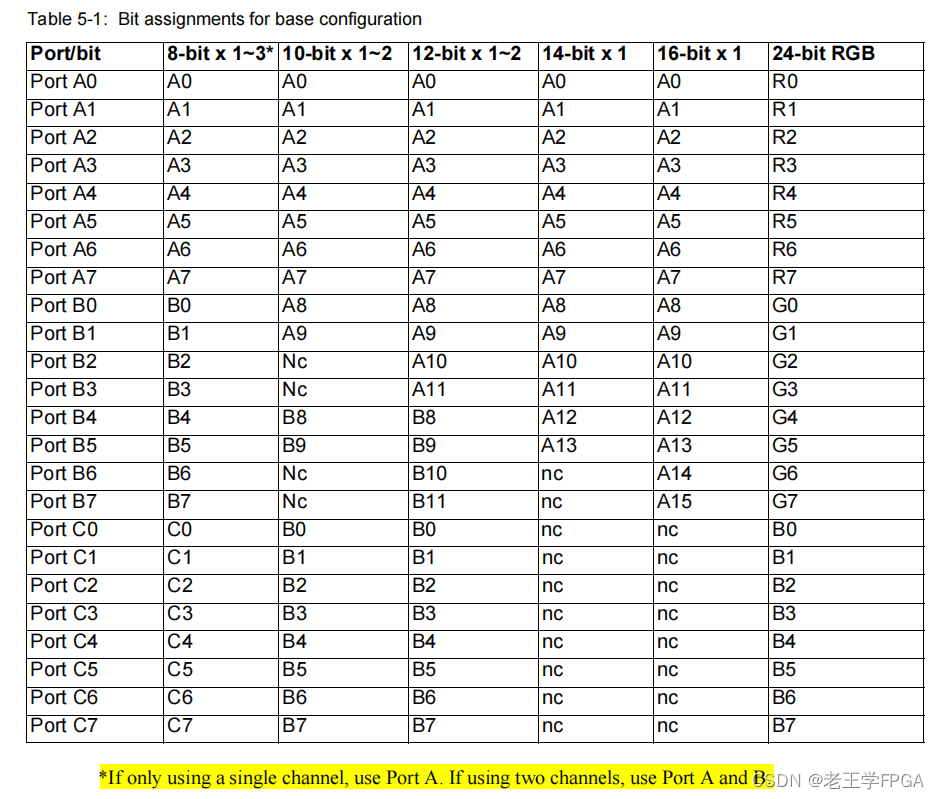

如上图所示,红圈处为base模式所涉及的信号,包括四路数据线和一路时钟线,都是差分的。portA、B、C ,DVAL、FVAl、LVAl等、是协议层面的信号,共28bit,而x0、x1、x2、x3对fpga来讲是实际的输出端口(实际上cameralink一开始就跟fpga没关系的,全篇协议内容都是配合收发芯片DS90CR284等来制定的)。但是对cmos或ccd来说输出的数据一般为8/12位的像素,那么这里涉及一个映射问题。这8/12bit数据是连接到portA呢还是B呢,抑或是随意连接呢?既然是协议,就要约定好了,cameralink给出了如下的约定。 如下图所示,按照表格进行信号的映射

以上是协议层面的映射,而涉及到传输链路的稳定及准确性,还要对总数为28bit的信号进行排序编码。与简单的按bit顺序编码不同,cameralink协议约定了一种特殊的顺序,这种编码结果可能是考虑到传输的稳定性和准确率。 如下如所示,即为cameralink的传输链路上的bit编码规则。

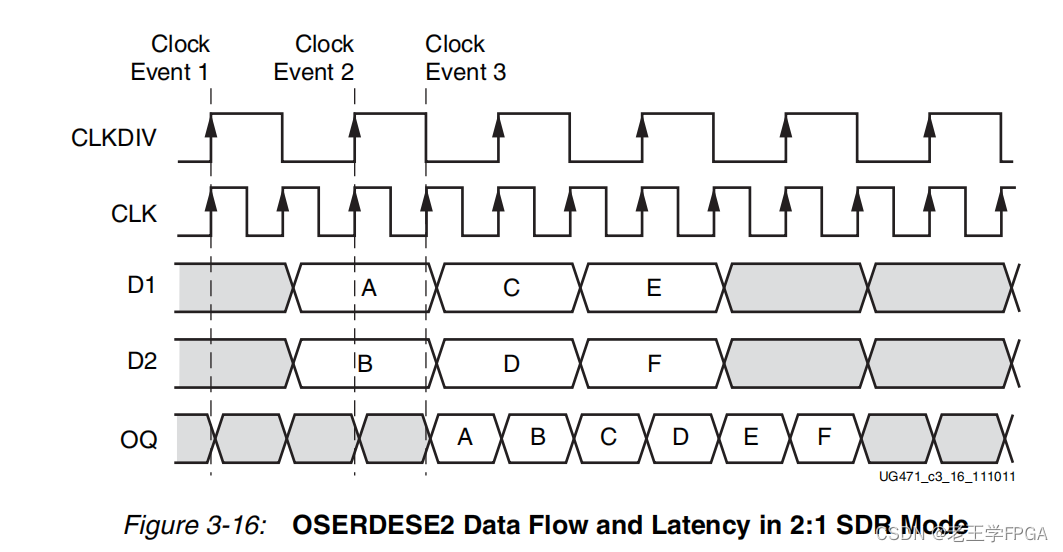

xilinx的7系列芯片具有很多IO资源,其中就包括OSERDES2资源,其功能是将并行数据串行化发出。cameralink的base模式通过4个数据通道将28bit的数据发出,因此需要使用4个串行化因子为7:1的OSERDES2资源。 如下图所示,即为其工作时序,详细说明可以阅读官方手册

colorbar 模块负责对应生成采图像素 clk_wiz0 模块例化了pll,生成慢速时钟40m以及快速时钟280m axi_stream_gen 负责产生行、场同步信号等图像控制信号 cameralink_coder 负责对28bits信号进行映射和编码 cameralinkTx 负责串行化发送 3 主要子模块分析 3.1 axi_stream_gen模块

产生 LVAL(tlast)、FVAL(tuser)、DVAL(tvaild)等图像控制信号。Hcnt、Vcnt 为行场计数,控制colorbar模块彩色块的产生。信号时序如下图。

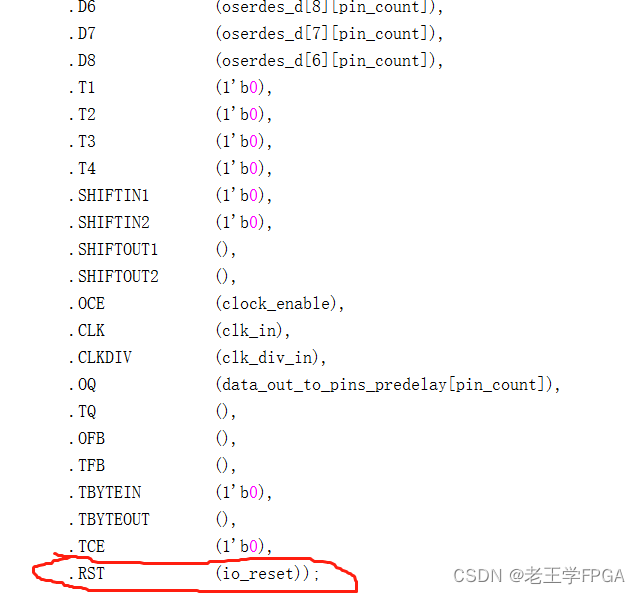

这个模块是例化了4路OSERDES2的原语,将28bit信号经4路通道串行发出,此外还利用OSERDES2生成了一路源同步时钟。 在编写此模块时,我们可以借助xilinx的selectio IP 来辅助生成。 将IP 配置成Cameralink Transmitter 模式,IO采用差分信号 。

创建IP后,打开IP的源码,可以复制过来当做CameralinkTx模块,不过要做些许修改。将DDR改成SDR,DATA_WIDTH 改成7,将D1-D7改成1100011即可。如下图。

连接cameralink采集卡,在camexpert 这个软件中配置成RGB模式,设置相应的参数,启动接收。测试结果如下,可见,可以正确接收到图片。

对于OSERDES2的RST端口,要等时钟稳定后,延时几个周期后再拉低。之前直接将此端口置0,一直仿真不出波形,这里是直接将PLL的locked信号取反连接到RST,解决了问题。

欢迎大家一块讨论分享分析,有不足之处也请多指正! |

【本文地址】