| 基于FPGA的实时JPEG编码器 | 您所在的位置:网站首页 › 1127055209_16122683179701n.jpg › 基于FPGA的实时JPEG编码器 |

基于FPGA的实时JPEG编码器

|

1 概述

JPEG,英文全称Joint Photographic Experts Group,即ISO和IEC联合图像专家组。这个专家组负责制定了静态图像压缩标准,即JPEG标准。

常用的JPEG压缩是有损压缩,但这个损失的部分是人的视觉不容易察觉到的部分,它充分利用了人眼对计算机色彩中的高频信息部分不敏感的特点,来压缩图像的原始信息。同时,图像本身也存在很大的信息冗余,数据之间存在着很大的相关性,因此可以利用这种信息相关性,进一步压缩图像数据。

下图是一个常用的JPEG baseline压缩编码器主要结构,本文从FPGA角度阐释如何实现JPEG实时编码。

2 JPEG Encoder系统介绍

JPEG压缩支持彩色域和灰度域,本文为简化设计,仅仅讨论灰度域实现。

FPGA逻辑主要实现图像数据8x8分块、离散余弦变换DCT、量化、Zigzag排序、Huffman编码。

2.1 8x8分块

JPEG编码是以8x8个像素点为一个块进行处理的,所以需要缓存完8行图像数据后,才可以开始处理。为了实现流水线处理,需采取乒乓操作。缓存完8行数据,开始做编码;同时开始缓存下一个8行,写乒的数据编码完,开始处理写乓的数据。

2.2 DCT变换

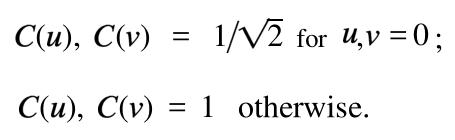

离散余弦变换DCT,是码率压缩中常用的一种变换编码方法。DTC变换的公式如下:

2.3 量化

DCT变换后,进行量化,量化即用DCT变换后的结果除以量化系数即可。标准中给出了参照的量化表,直接引用即可。采用Xilinx提高的除法器IP核实现。压缩比很大程度由量化表的数值决定。

2.4 Zigzag扫描

量化后的8x8块系数,采用Zigzag扫描,对数据进行重排序。

2.5 Huffman编码

Zigzag数据重排序后,对64个数据进行遍历,同时进行DC差分编码和AC行程编码。DC和AC编码要对8x8块的64个数做遍历,遍历完,行程编码完成,写入Ram,且若最后为全0(EOB),要对最后一个数做修正处理。所以,处理一个8x8块的行程编码最少时钟为64+N。处理完,再循环。

行程编码后,每8x8块转换成一个个的数据对,再对应Huffman表,将每个单元对转成二进制码流,以字节为单位输出,即可。

3 该编码器优势 (1)实时可编程量化表,压缩比1:2~1:10可调; (2)实时可调图像分辨率,最大图片分辨率8kx8k; (3)实时编码,图片分辨率8kx8k,实时帧频可达到2frame/s;1280x720分辨率下实时编码效率可达到200frame/s。 (4)默认Mono域; (5)主流FPGA(Xilinx, Altera)均可移植,在Xilinx K7325t上实现; (6)默认数据接口AXI4,数据位宽8bits,数据通道8tap,配置接口AXI Lite。 欢迎关注我的微信公众号:FPGA干货架

|

【本文地址】