| 解析计算机体系结构中的MACs实现 | 您所在的位置:网站首页 › macbook更新换代频率 › 解析计算机体系结构中的MACs实现 |

解析计算机体系结构中的MACs实现

|

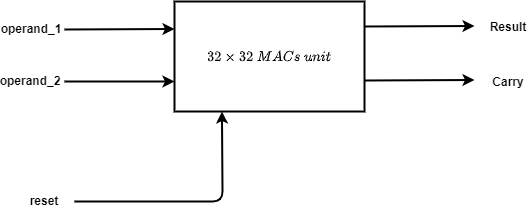

矩阵乘法包含大量的a+b*c类运算,因此常在运算中将乘法器和加法器合成一个计算单元,进程乘法累加操作,这个单元被称为MACs(multiply and accumulate operations.MAC).乘法运算是数学中重要的基本算术运算,乘法累加操作在数字信号处理中被广泛应用,比如,FFT,DFT,卷积计算,甚至是微控制器的ALU中的通用计算单元都能见到它的身影。在DSP应用中,比通用处理器更加侧重MACs的设计,MACs的逻辑实现通常是数字电路设计中Critical path的主要贡献方,设计的好坏决定了PPA,本文试图从软件视角搞清楚MACs是什么以及如何工作的。 设计原理MACs顶层实现方框图如下,其中的operand_1 和 operand_2是32位输入操作数,MACs操作的结果通过64位的Result pin输出,内部的64位加法器将乘法器的输出作为第一个操作数,与存储在内部的第二个加法操作数相加,第二个操作数的来源一般是上一个周期的Result结果,得到Result输出和进位信号Carry,这里的32x32表示两32位输入的MAC,并非是乘法,也并非代表个数,如果N个这样的MAC,一般表示为N*32x32MAC.

|

【本文地址】

公司简介

联系我们