| 基于FPGA的4位十进制密码锁VHDL代码Quartus仿真 | 您所在的位置:网站首页 › fpga密码锁代码 › 基于FPGA的4位十进制密码锁VHDL代码Quartus仿真 |

基于FPGA的4位十进制密码锁VHDL代码Quartus仿真

|

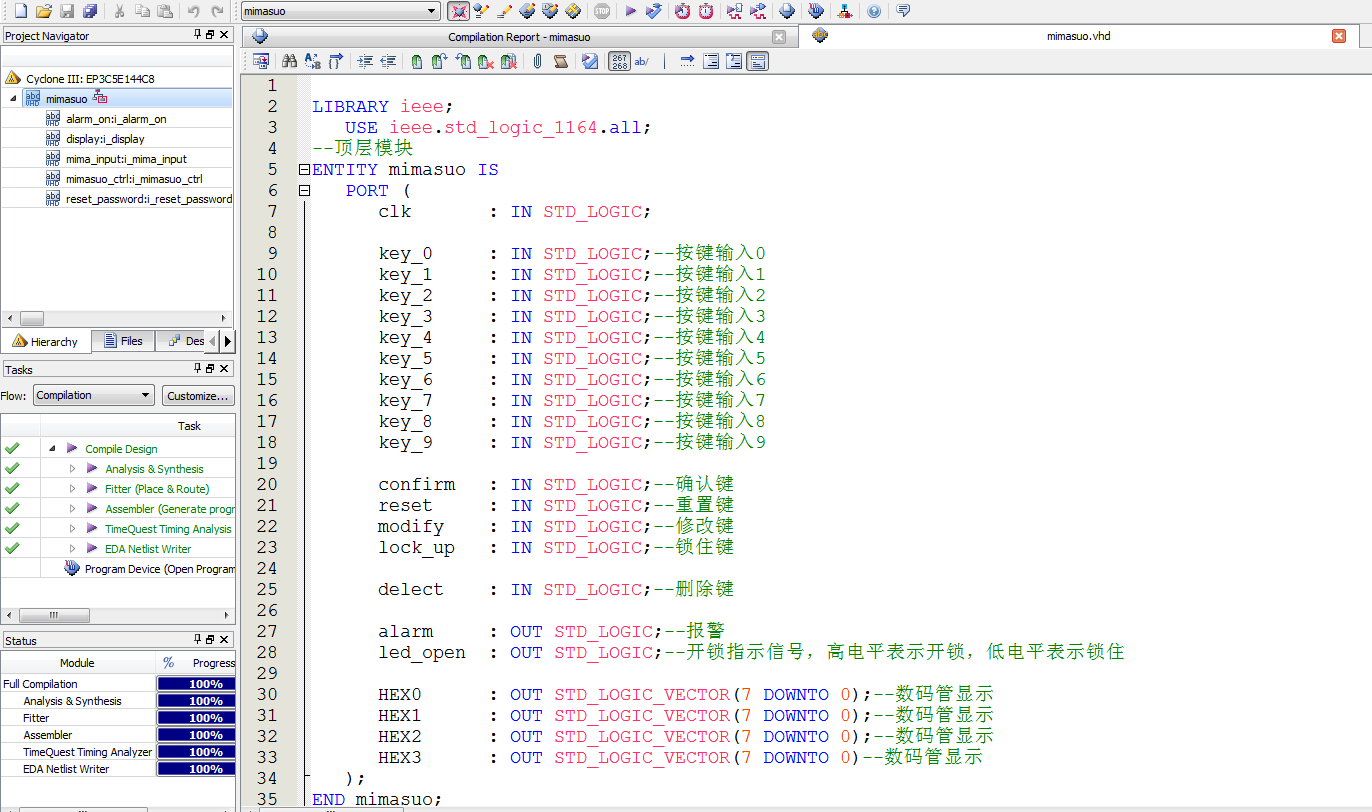

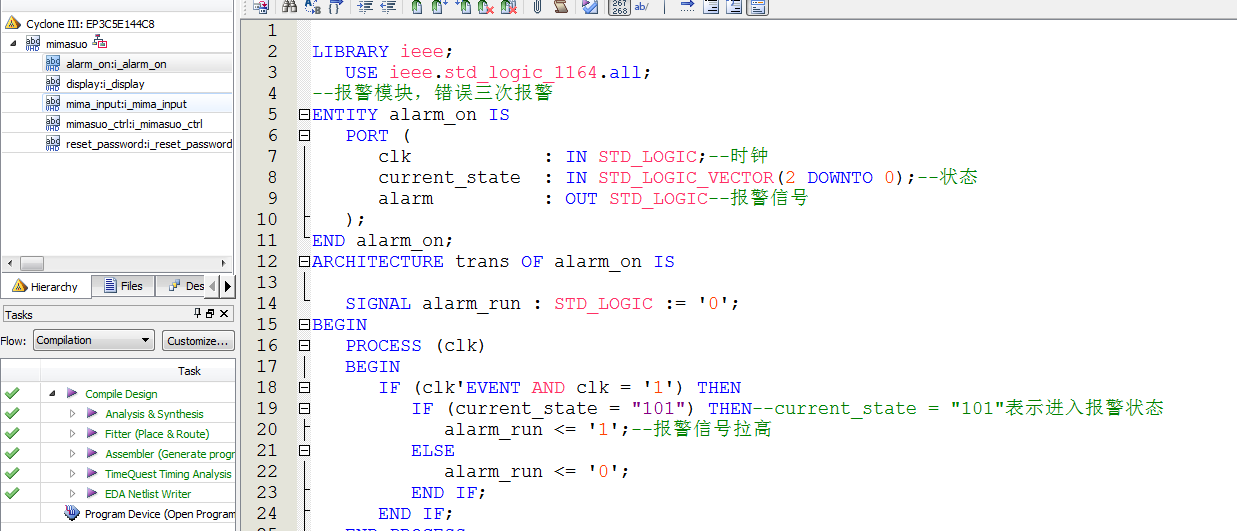

名称:基于FPGA的4位十进制密码锁VHDL代码Quartus仿真(文末获取) 软件:Quartus 语言:VHDL 代码功能: 4位十进制密码锁 1、可以输入0~9个数字 2、密码为4位,输入错误可以删除 3、密码正确led提示开锁,密码错误达3次报警 4、可以通过按键修改密码 1. 工程文件

2. 程序文件

3. 程序编译

4. RTL图

5. Testbench

6. 仿真图 整体仿真图

显示模块

密码输入模块

密码锁控制模块

密码修改模块

部分代码展示: LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; --密码输入模块 ENTITY mima_input IS PORT ( clk : IN STD_LOGIC; key_0 : IN STD_LOGIC;--按键0 key_1 : IN STD_LOGIC;--按键1 key_2 : IN STD_LOGIC;--按键2 key_3 : IN STD_LOGIC;--按键3 key_4 : IN STD_LOGIC;--按键4 key_5 : IN STD_LOGIC;--按键5 key_6 : IN STD_LOGIC;--按键6 key_7 : IN STD_LOGIC;--按键7 key_8 : IN STD_LOGIC;--按键8 key_9 : IN STD_LOGIC;--按键9 delect : IN STD_LOGIC;--删除键 current_state : IN STD_LOGIC_VECTOR(2 DOWNTO 0);--当前状态 password : OUT STD_LOGIC_VECTOR(15 DOWNTO 0)--4位密码,用BCD码表示,一共16位 ); END mima_input; -- current_state=3'd0;锁住 -- current_state=3'd1;密码比对 -- current_state=3'd2;开锁 -- current_state=3'd3;密码错误 -- current_state=3'd4;修改密码 -- current_state=3'd5;报警 ARCHITECTURE trans OF mima_input IS --定义中间信号 SIGNAL current_num_buf : STD_LOGIC_VECTOR(2 DOWNTO 0):="000";--当前输入密码个数 SIGNAL delect_buf1 : STD_LOGIC := '0'; SIGNAL delect_buf2 : STD_LOGIC := '0'; SIGNAL key_0_buf1 : STD_LOGIC := '0'; SIGNAL key_1_buf1 : STD_LOGIC := '0'; SIGNAL key_2_buf1 : STD_LOGIC := '0'; SIGNAL key_3_buf1 : STD_LOGIC := '0'; SIGNAL key_4_buf1 : STD_LOGIC := '0'; SIGNAL key_5_buf1 : STD_LOGIC := '0'; SIGNAL key_6_buf1 : STD_LOGIC := '0'; SIGNAL key_7_buf1 : STD_LOGIC := '0'; SIGNAL key_8_buf1 : STD_LOGIC := '0'; SIGNAL key_9_buf1 : STD_LOGIC := '0'; SIGNAL key_0_buf2 : STD_LOGIC := '0'; SIGNAL key_1_buf2 : STD_LOGIC := '0'; SIGNAL key_2_buf2 : STD_LOGIC := '0'; SIGNAL key_3_buf2 : STD_LOGIC := '0'; SIGNAL key_4_buf2 : STD_LOGIC := '0'; SIGNAL key_5_buf2 : STD_LOGIC := '0'; SIGNAL key_6_buf2 : STD_LOGIC := '0'; SIGNAL key_7_buf2 : STD_LOGIC := '0'; SIGNAL key_8_buf2 : STD_LOGIC := '0'; SIGNAL key_9_buf2 : STD_LOGIC := '0'; SIGNAL key_0_rise : STD_LOGIC; SIGNAL key_1_rise : STD_LOGIC; SIGNAL key_2_rise : STD_LOGIC; SIGNAL key_3_rise : STD_LOGIC; SIGNAL key_4_rise : STD_LOGIC; SIGNAL key_5_rise : STD_LOGIC; SIGNAL key_6_rise : STD_LOGIC; SIGNAL key_7_rise : STD_LOGIC; SIGNAL key_8_rise : STD_LOGIC; SIGNAL key_9_rise : STD_LOGIC; SIGNAL delect_rise : STD_LOGIC; SIGNAL password_buf : STD_LOGIC_VECTOR(15 DOWNTO 0) := "0000000000000000"; BEGIN --信号缓存 源代码扫描文章末尾的公众号二维码 |

【本文地址】

公司简介

联系我们