| DDR3、DDR3L以及LPDDR3对比介绍,规范解读以及硬件设计开发实际案例分享 | 您所在的位置:网站首页 › ddr3和ddr3l混用的后果 › DDR3、DDR3L以及LPDDR3对比介绍,规范解读以及硬件设计开发实际案例分享 |

DDR3、DDR3L以及LPDDR3对比介绍,规范解读以及硬件设计开发实际案例分享

|

本文主要是由一个问题引起,关于Zynq 7000系列芯片是否支持LPDDR3。Zynq7000是不支持LPDDR3应用的,还有一些特殊形式的Dual-die / Quad-die这种形式的DDR3颗粒也不支持。本文主要围绕DDR3、DDR3L以及LPDDR3的JTSD标准解读,实际的设计案例分享。本号有非常多的实际设计案例分享文章,欢迎阅读。

本博客精品文章主要内容如下: Zynq7000硬件开发之硬件开发流程简介(一)https://blog.csdn.net/bianyuanren92/article/details/119608462?spm=1001.2014.3001.5501 Zynq7000硬件开发之总体硬件架构设计 Zynq硬件开发之Xilinx官方技术手册解读(一) Zynq7000硬件开发之Xilinx官方技术手册解读(二) Zynq7000硬件开发之芯片供电电源功耗(电流)评估_硬件开发不完全攻略-CSDN博客案头语:单板硬件的主控芯片集成度越来越高,多核处理器越来越多,一块单板可能只需要1块芯片就能满足整体需求,一方面减少设计复杂度、另一面节省PCB面积成本,能同时掌握硬件原理设计以及PCB Layout设计逐渐成为主流,本系列文章同时包含有两部分内容且进行融合,欢迎大家持续关注,关注微信公众号“硬件开发不完全攻略”。 本次更新内容主要讲述如何通过Zynq 7000在Vivado下的工程文件评估芯片的各路电源功耗(电流),电源功耗(电流)评估对于电源选型、电源平面设计、电源完整仿真评估等都有很重... Zynq7000硬件开发之电源供电系统(PDN)设计(一)https://blog.csdn.net/bianyuanren92/article/details/120032000?spm=1001.2014.3001.5501 DDR3参考标准为JESD79-3F,其中F为版本号,由JEDEC协会(固态技术协会)发布的标准,各个DDR生产厂家产品都必须满足,所以只要DDR的参数相同,各个厂家的器件均可直接替代,单片最大容量为8Gb。小编也积累了一些DDR的标准,有DDR, DDR2, DDR3,DDR4, GDDR5, LPDDR2, LPDDR3, LPDDR4,文后附有下载方式。

DDR3L参考标准为JESD79-3-1A,一般来讲DD3L产品都会反向兼容DDR3系列产品,不同点为DDR3供电为1.5V、DDR3L为1.35V。下图为某厂家的DDR3L颗粒的描述。

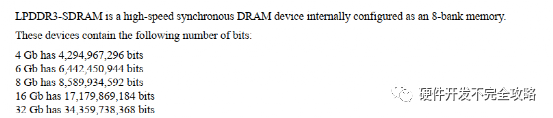

LPDDR3为LPDDR(Low Power Double Data Rate SDRAM)系列中的产品,参考标准为JESD209-3B,主要面向低功耗内存而制定的通信标准,以低功耗和小体积著称,专门用于移动式电子产品,最大容量为32Gb,是DDR3的4倍。 LPDDR3有POP堆叠封装和独立封装形式,堆叠封装包含有“球-焊盘”和“球-球”两种,具体图如下:

图片来源网络,POP封装的两种形式

DDR3有多晶片(Die)产品,分为Dual-die和Quad-die产品,与单die产品区别为CKE, /CS,ODT,ZQD等信号数量不同。

DDR3与LPDDR3的数据部分管脚定义无明显差别,只是LPDDR3单颗粒支持最大数据宽度为32位,分为4组数据信号,单组数据信号均包括DQ1-8, DQS+/-, DM等;控制以及地址信号定义差别较大,具体如下 DDR3管脚定义(以单die x16 96ball为例)如下:

LPDDR3管脚定义如下:

DDR3的A0-A14, RAS#, CAS#, WE#,BA0-2这些信号在LPDDR3中改为了CA0-9,主要原因是两种芯片的Command truth table的定义更改了,对于内置有DDR控制器的处理器来说,硬件和软件设计时只要对相应管脚的定义准确即可,具体操作有DDR控制器处理,具体区别如下 DDR3 的Command truth table

LPDDR3 的Command truth table

Zynq7000的DDR3设计原理图如下所示,其支持DDR3/DDR3L,但支持不了Dual-die、Quad-die的DDR3芯片。设计为2片X16的DDR3,Fly-by连接形式,具体如下。

LPDDR3设计为RK3399芯片的外部存储,其包含2个DDR控制器,可支持DDR3, LPDDR3, 以及Dual-die/Quad-die DDR3颗粒,具体设计如下,另一DDR控制器设计相同,设计为x32位LPDDR3颗粒。

LPDDR3 颗粒型号为K4E8304EE-EGCE,型号具体参数如下:

另外LPDDR3与DDR3的封装形式也有较大差异,具体可参考JESD-DDR系列标准。 关注微信公众号“硬件开发不完全攻略”,后台回复“DDR标准”获取JESD-DDR系列标准,仅供学习交流使用。如需官方文件,请在JEDEC协会官网下载获取。 |

【本文地址】